# Degradation mechanisms and lifetime assessment of Ge Vertical PIN photodetectors

Kristof Croes, Veerle Simons, Brecht Truijen, Philippe Roussel, Koen Van Sever, Artemisia Tsiara, Jacopo Franco and Philippe Absil

imec, Kapeldreef 75, 3000, Leuven, Belgium e-mail: kristof.croes@imec.be

**Abstract:** Dark current degradation mechanisms in Ge VPIN photodetectors were studied. A methodology to estimate the failure percentages has been developed and applied. Degradation/recovery processes and  $E_a$ -decrease of  $I_{dark}$  after stress suggest increased TAT during degradation.

#### 1. Introduction

Optical receivers based on high opto-electrical bandwidth, high responsivity and low  $I_{dark}$  waveguide-coupled Ge Vertical PIN photodetectors (PD), substantially enhance the performance of Si-based optical interconnects [1], where the performance of these PDs have been boosted by recent achievements in the epitaxial growth of Ge on Si. During operation, at nominal conditions, Ge PDs are reverse biased at -1V or -2V, and their dark current,  $I_{dark}$ , needs to remain sufficiently low to ensure a high signal-to-noise ratio of the optical receiver". The degradation mechanisms that drive the increase of  $I_{dark}$  are very complex [2-3]. This paper addresses a methodology to estimate failure rates of these components and digs deeper in the fundamentals of the degradation mechanisms.

#### 2. Studied device and measurement methodology

We focus on vertical p-i-n waveguide-coupled Ge VPIN PDs of 2μm width, 400nm height and 13.7μm length. The doping profile in Ge was optimized for high-speed operation and low series resistance. Devices were fabricated using imec's 200 mm silicon photonics platform [4].

$I_{dark}$  characterization and degradation was performed on imee's Process Control Monitor devices, where no circuitry was connected to the devices. Long-term stresses were enabled by dicing and wire bonding the devices in a ceramic package. The packages were then loaded in our in-house package level reliability tester where voltages can be applied and currents can be measured as a function of time at temperatures up to  $200^{\circ}$ C.

### 3. Lifetime assessment methodology

A methodology to estimate failure percentages of our devices has been developed and applied. We first propose ways to estimate temperature and voltage acceleration factors and then propose a method to estimate failure percentages at given use conditions.

## 3.1. Temperature acceleration

First, the temperature acceleration factor has been estimated using tests at different temperatures. An Arrhenius dependence of degradation with temperature T is assumed:

Time

$$\sim \exp(E_a/(k_B*T)),$$

(1)

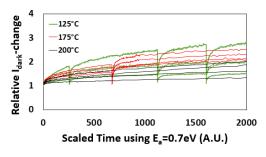

wherein  $E_a$  is the activation energy of degradation and  $k_B$  is Boltzmann's constant. To estimate  $E_a$ , tests at three different temperatures were performed at 2V (which is  $2xV_{op}$  for  $V_{op}=1V$  and is consistent with Telcordia [5]), where  $I_{dark}$  was measured as a function of time. Figure 1a shows the relative  $I_{dark}$  change as a function of time. In order to quantify the  $E_a$  of degradation, the x-axis has been scaled using equation (1) in a way that the degradation curves from different temperatures fall on top of each other as well as possible. For this data set, the best match was with  $E_a=0.7eV$ .

#### 3.2. Voltage acceleration

Second, the voltage acceleration factor has been estimated. A power law degradation with voltage V is assumed:

Time

$$\sim V^{\rm m}$$

, (2)

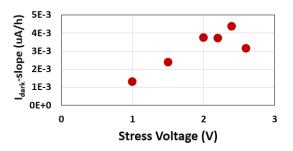

wherein m is the voltage acceleration factor. To estimate m, a step stress was performed. During this test, the  $I_{dark}$  at  $175^{\circ}$ C of a number of devices was monitored. First, 1V was applied for 100h, then 1.5V applied for 100h, etc. Figure 1b shows the slope of a linear fit of the  $I_{dark}$  increase as a function of voltage. Between 1 and 2V, a linear increase of the  $I_{dark}$ -slope with voltage is observed with a 2.7-3.2x faster degradation at 2V stress compared to 1V.

Fig. 1a: Relative  $I_{dark}$ -change with time for devices stressed at different temperatures. X-axis is scaled using eq. (1) with  $E_a$ =0.7eV

Fig. 1b: I<sub>dark</sub>-slope as a function of stress voltage during a step stress at 175°C

Note that above 2V no further increase of the  $I_{dark}$ -slope is observed. We hypothesize that this observation is linked to the specific characteristics of the degradation curves of our devices (Figure 1a) where an initial faster increase of  $I_{dark}$  is observed. We argue that the slopes at voltages >2V have been obtained in the degradation region where the  $I_{dark}$ -increase was already in the later phase leading to artificially lower  $I_{dark}$ -slopes at these voltages.

#### 3.3. Lifetime prediction methodology

Using the acceleration factors estimated in the previous section, a 3-step lifetime prediction methodology is proposed:

1. Given  $T_{op}$  and  $V_{op}$ , calculate the stress time  $t_{stress}$  at 175°C-2V (proposed  $T_{stress}$  and  $V_{stress}$  by TELCORDIA [5]) that is needed to mimic the required lifetime  $t_{req}$  for a certain application. This is done by plugging in the  $E_a$  and m obtained in the previous sections in formulas (1) and (2):

$$t_{stress} = t_{req} * (V_{op}/V_{stress})^{m} * exp(E_a/k_B * (1/(T_{stress} + 273) - 1/(T_{op} + 273))$$

(3)

An example for a specific case is worked out in table 1.

Table 1. Example of t<sub>stress</sub>-calculation (E<sub>a</sub>=0.6eV and m=2.5 is used as conservative estimates of the acceleration factors)

| $T_{op}$ | $V_{op}$ | $t_{\rm req}$ | <br>t <sub>stress</sub> |

|----------|----------|---------------|-------------------------|

| 90°C     | 1V       | 5y            | 460h                    |

- 2. Stress a number of devices for  $t_{stress}$  at 175°C-2V and measure the  $I_{dark}$  at  $V_{op}$  and  $T_{op}$  after stress.

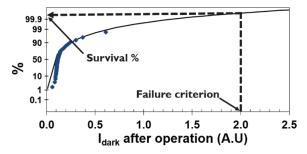

- Make a cumulative plot of the obtained I<sub>dark</sub> or of the obtained I<sub>dark</sub>-change and determine the survival % using a given failure criterion (Figure 2). Determination of the survival % might require a bimodal fit for certain data sets.

Fig. 2: Probability plot of the measured  $I_{dark}$  at  $V_{op}$  and  $T_{op}$  after stressing at 175°C-2V during  $t_{stress}$  + bimodal fit of the data

#### 4. Degradation mechanisms

We also looked into the fundamentals of the  $I_{dark}$  degradation in our devices where we addressed the impact of voltage stress on  $I_{dark}$ - $E_a$  and where we looked into possible recovery effects.

#### 4.1. Lowering of $I_{dark}$ activation energy

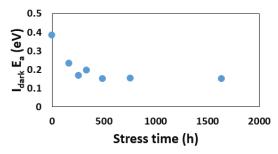

A lowered  $I_{dark}$ - $E_a$  with stress time is observed, where an initial median  $E_a$  of ~0.4eV lowers to a median  $E_a$  of <0.2eV after a few 100h of stress (see figure 3). The saturating behavior over time is consistent with the saturation of the  $I_{dark}$ -increase during stress (figure 1a). The lowering of the  $I_{dark}$ - $E_a$  is consistent with earlier reports and is potentially linked to an increased contribution of trap-assisted-tunneling to the conduction at the Ge/Si and Ge/O<sub>x</sub> interfaces [2],[6].

#### 4.2. Recovery effect

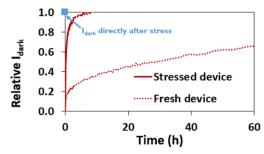

After stress, when the voltage is switched to 0V, a recovery of  $I_{dark}$  is observed, where for our devices an apparent recovery happens after a few hours. Figure 4 shows that, when switching on the voltage again, the  $I_{dark}$  immediately starts to increase at a faster rate compared to a fresh device (dashed versus solid line). The physics of this phenomenon could be related to the creation and passivation of dangling bonds at the earlier mentioned Ge/Si and Ge/Ox interfaces and is subject of further study.

Fig. 3:  $I_{dark}$ - $E_a$  as a function of stress time

Fig. 4: I<sub>dark</sub> vs time at 200°C-2V of a stressed and a fresh device after a couple of hours relaxation at 0V

#### 5. Conclusions

We looked in the fundamentals of the degradation mechanisms in Ge VPIN photodetectors.

First, we established a methodology to characterize failure percentages. This happened in 5 steps:

- 1. Estimation of temperature acceleration by fitting data at various temperatures to the Arrhenius equation. For our data set, we estimated an E<sub>a</sub> of ~0.7eV.

- 2. Estimation of voltage acceleration using a step stress and by assuming a power law dependence of time on voltage. For our data set, we estimated an estimated acceleration factor of 2.7-3.2x between 1 and 2V.

- 3. Calculate the  $t_{stress}$  at  $175^{\circ}\text{C}$ -2V that is needed to mimic the required lifetime  $t_{req}$  for a certain application using  $t_{req}*(V_{op}/V_{stress})^{m}*\exp(E_a/k_B*(1/(T_{stress}+273)-1/(T_{op}+273))$ .

- 4. Stress a number of devices for  $t_{\text{stress}}$  and measure the  $I_{\text{dark}}$  at  $V_{\text{op}}$  and  $T_{\text{op}}$  after stress.

- 5. Make a cumulative plot of the obtained  $I_{dark}$  or  $I_{dark}$ -change and determine the survival percentages.

Second, we hypothesized that a decreasing  $I_{dark}$ - $E_a$  with stress time was linked to an increased contribution of trapassisted-tunneling to the conduction at the Ge/Si and Ge/Ox interfaces.

Finally, we observed a recovery effect of  $I_{dark}$ , where for our devices an apparent recovery happens after a few hours. The phenomenon is only partial in so far that the  $I_{dark}$  increase after recovery goes at a faster rate compared to a fresh device.

## 6. References

- [1] Ph. Absil, K. Croes, A. Lesniewska, P. De Heyn, Y. Ban, B. Snyder, J. De Coster et al. "Reliable 50Gb/s silicon photonics platform for next-generation data center optical interconnects." In Electron Devices Meeting (IEDM), 2017 IEEE International, pp. 34-2

- [2] A. Leśniewska, S. A. Srinivasan, J. Van Campenhout, B. J. O'Sullivan, K. Croes, "Accelerated Device Degradation of High-Speed Ge Waveguide Photodetectors", In Reliability Physics Symposium (IRPS), 2019 IEEE International, pp. 4A\_3

- [3] S. Rauch, D. Lee, A. Vert, B. Min, "Reliability Failure Modes of an Integrated Ge Photodiode for Si Photonics", 2020 Optical Fiber Communications Conference and Exhibition (OFC), pp. W2A.5

- [4] M. Pantouvaki, S.A. Srinivasan, Y. Ban, P. De Heyn, P. Verheyen, G. Lepage, et al. (2017). "Active components for 50 Gb/s NRZ-OOK optical interconnects" in a silicon photonics platform. Journal of Lightwave Technology, 35(4), 631-638.

- [5] Telcordia Technologies Generic Requirements GR-486-CORE (2004)

- [6] E. Simoen, F. De Stefano, G. Eneman, B. De Jaeger, C. Claeys and F. Crupi (2009). On the Temperature and Field Dependence of Trap-Assisted Tunneling Current in Ge+n Junctions. IEEE Electron Device Letters, 30(5), 562-564.