M3D.3.pdf OFC 2020 © OSA 2020

# Ultra-Thin III-V Photodetectors Epitaxially Integrated on Si with Bandwidth Exceeding 25 GHz

Svenja Mauthe<sup>1</sup>, Yannick Baumgartner<sup>1</sup>, Saurabh Sant<sup>2+</sup>, Qian Ding<sup>2</sup>, Marilyne Sousa<sup>1</sup>, Lukas Czornomaz<sup>1</sup>, Andreas Schenk<sup>2</sup>, and Kirsten E. Moselund<sup>1</sup>

<sup>1</sup> IBM Research – Zurich, Säumerstrasse 4, 8803 Rüschlikon, Switzerland.

<sup>2</sup> ETH Zurich, Department of Information Technology and Electrical Engineering, Gloriastrasse 35, 8092 Zürich, Switzerland.

<sup>+</sup> now at Infineon Technologies AG Munich, Germany.

sym@zurich.ibm.com

**Abstract:** We demonstrate the first local monolithic integration of high-speed III-V p-i-n photodetectors on Si by in-plane epitaxy. Ultra-low capacitance permits data reception at 32Gbps. The approach allows close integration to electronics enabling future receiverless communication. © 2020 The Author(s)

OCIS codes: 040.5160, 130.0250, 130.5990.

### 1. Introduction

Si photonic integrated circuits (PICs) have sparked great interest due to the promise of combining the improved bandwidth and integrity of optical signals with the dense integration of electronics. The synergy with CMOS enables a combination of the best properties of both worlds: sophisticated Si electronics along with mature CMOS fabrication technology combined with high-speed, low loss, and low power optical communication. A key component of an alloptical link is a high-speed, low power photodetector (PD) operating in the O- and C-bands. Key to achieve both, high-speed and low-power operation is a close integration to Si electronics as well as scaled devices with ultra-small capacitance [1].

Scaled high-performance Ge PDs on Si have already been demonstrated showing high bandwidths, although potentially suffering from higher dark currents and lower absorption in the C-band [2]. III-V materials are promising materials due to their high absorption coefficients and direct tunable bandgap which allows for both efficient detection and emission, but are very challenging to integrate on Si due to a large lattice and thermal mismatch. A competitive approach to integrate III-Vs on Si is wafer bonding since it allows for extensive optimization of the III-V stack on the growth wafer before transfer, such as the incorporation of quantum wells, and promising results have been demonstrated [3]. Wafer bonding however, is limited to the size of the III-V wafer. Moreover, for fully integrated electro-optical systems, the ultimate goal for high-speed PDs is a direct, local, and epitaxial integration. One promising approach are epitaxial III-V nanowires on Si. High crystalline quality can be achieved, however usually the device design is limited by a vertically oriented high-aspect ratio design or are based on pick-and-place techniques [4-6]. Moreover, to the best of our knowledge, high-speed data detection (>10 GHz) with nanowire PDs has not been demonstrated yet.

In this paper, we report the first laterally and epitaxially integrated ultra-thin III-V p-i-n nanostructure PD on Si. The devices show a 3-dB bandwidth exceeding ~25 GHz with high responsivity in the O-band and a sub-fF capacitance data reception up to 32 Gbps On-Off Keying (OOK).

## 2. Concept and Fabrication

We propose a laterally integrated III-V p-i-n PD directly grown on Si by template-assisted selective epitaxy (TASE [7-9]). Compared to standard fabrication processes, like e.g. bonding, the PDs are directly grown from a Si seed in horizontal direction allowing for the future in-plane integration with Si electronics and passives. This enables the future direct butt-coupled integration to a Si waveguide. The III-V material is epitaxially grown starting from a standard silicon-on-insulator substrate (SOI). The top Si layer is patterned, covered with oxide, and the Si subsequently partially etched. The resulting structure is a predefined hollow SiO<sub>2</sub> template with a confined Si seed on one end and an opening on the other end. Finally, In<sub>0.5</sub>Ga<sub>0.5</sub>As is grown starting from the Si seed using metal-organic chemical vapor deposition (MOCVD) at 550 °C. The confined interface with the Si seed results in single crystalline material. By adding dopant precursors during the growth, an in-situ p-i-n doping profile is obtained along the growth direction as indicated in Fig. 1a. The position of the p-i-n interfaces is controlled by the growth time during the single growth step. This enables the fabrication of extremely scaled devices since no post processing like, diffusion or implantation

M3D.3.pdf OFC 2020 © OSA 2020

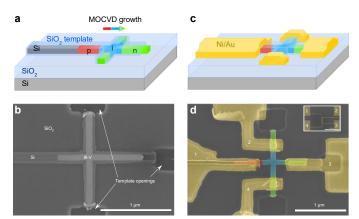

Fig. 1: (a) Schematic of a p-i-n cross-bar directly grown on Si using TASE. The arrow indicates the growth direction during MOCVD growth. (b) SEM image of a p-i-n InGaAs structure. (c) Schematic of a p-i-n cross-bar with electrical contacts. (d) SEM image of a contacted p-i-n device. Inset shows an SEM overview of a p-i-n device with contacts and contact pads.

doping, or epitaxial regrowth is required. Since the growth starts at the Si seed, the structure exhibits one p-doped region and three n-doped regions at the three extremities with openings in the  $SiO_2$  template. Fig. 1b shows scanning electron microscopy (SEM) image of a p-i-n device grown in a cross-bar shape. Devices are as thin as ~60 nm, exhibit a length of ~1  $\mu$ m and are varied in width from 60 nm to 500 nm, resulting in devices with ultra-low footprints of the entire device as low as 0.06  $\mu$ m<sup>2</sup>. Devices are contacted on all four ends using Ni/Au lift-off contacts (see Fig. 1c). Fig.1d shows an SEM image of a contacted device.

## 3. Electrical Characterization and Dynamic Measurements

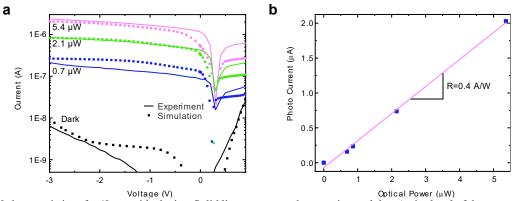

To quantify the performance of the PDs we perform both static and dynamic measurements. Due to constraints imposed by the contact pads design and RF probes, measurements were performed on cross-type structures between contact 1 and 4 (see Fig. 1d). First, the dark current is measured as 850 pA at -1.5 V reverse bias for a 60 nm wide single crystalline device. Next, the devices are illuminated from the top using a single mode fiber and a continuous wave laser. Wavelength dependent IV-measurements are performed between 1200 nm and 1700 nm revealing light detection both in the O- and C-band with a maximum absorption at 1346 nm. Fig. 2a depicts both, DC measurements in dark and under varying illumination powers of the 1346 nm laser (solid line) overlaid with simulated curves (dotted line). With increasing optical power, the current in reverse bias increases following expected diode behavior resulting in a responsivity of ~0.4 A/W at -2 V applied bias (see Fig. 2a and b). The responsivity was calculated using the measured photo current and the calculated incident optical power on the active device area. Electro-optical simulations confirm the measured IV characteristics and reveal a Schottky barrier height of 0.3 eV [10].

To confirm the high-speed nature of the nanowire PDs, bandwidth measurements using a vector network analyzer and a commercial 32 Gbps lithium niobate modulator are conducted. Fig. 3a shows the frequency response of a 60 nm

Fig. 2: (a) IV characteristics of a 60 nm wide device. Solid lines represent the experimental data (noise level of the setup: ~500 pA), dotted lines are obtained by performing simulations using Synopsys Sentaurus simulation software [10]. (b) Photo current at -2 V plotted via incident optical power on the 60 nm wide device. The slope reveals a responsivity of ~0.4 A/W.

M3D.3.pdf OFC 2020 © OSA 2020

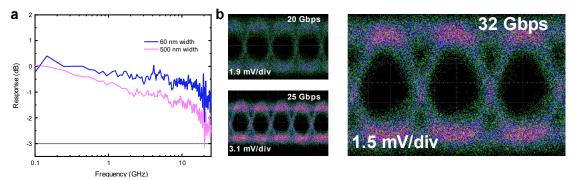

Fig. 3: (a) Frequency response ( $S_{21}$ ) of a 60 nm and 500 nm wide device. The solid line at -3 dB indicates the 3-dB limit. (b) Eye diagrams at 20, 25, and 32 Gbps OOK measured on a 500 nm wide device (V = -2 V, no pre-emphasis, 20 ps/div).

and 500 nm wide device when illuminated with a modulated optical signal at 1346 nm. Both devices show a frequency response beyond our measurement capabilities (~25 GHz).

Fig. 3b and c depict eye-diagrams at 20, 25, and 32 Gbps measured on the 500 nm wide device. An OOK pseudo random binary sequence (PRBS, 2<sup>7</sup>-1 bits) is sent onto the PDs at the determined maximum of detection (1346 nm). The eye diagrams show a clear opening at high data rates and hence, confirm the high-speed operation of the presented devices.

### 4. Conclusion

We demonstrated for the first time high-speed detection in the O-band based on a monolithic in-plane p-i-n PD based on direct epitaxy on Si. The unique integration approach allows for the direct epitaxial growth of ultra-thin III-V PDs in lateral direction (~60 nm) with in-situ doping profiles and total device footprints as low as 0.06 µm². Devices show low dark currents of 850 pA at -1.5 V bias and a responsivity of 0.4 A/W at -2 V. High-speed data detection is tested confirming 32 Gbps OOK signal detection and a RF response up to 25 GHz. Due to the direct growth on Si, future devices can be directly grown onto Si waveguides enabling an optical link with direct coupling. Moreover, the fabrication technique allows for a close integration to Si electronics and hence, lays the foundation for future low-power receiverless communication.

## 5. Acknowledgment

We received financial support from H2020 ERC project PLASMIC grant no. 678567 and H2020 project DIMENSION grant no. 688003. We acknowledge E. Salis, H. Schmid, M. D. Rossell, and J. Leuthold for technical discussions and assistance.

### 6. References

- [1] D. A. B. Miller, "Attojoule Optoelectronics for Low-Energy Information Processing and Communications," J. Light. Technol., vol. 35, no. 3, pp. 346–396, 2017.

- [2] S. Lischke et al., "High bandwidth, high responsivity waveguide-coupled germanium p-i-n photodiode," Opt. Express, vol. 23, no. 21, p. 27213, 2015.

- [3] Y. Baumgartner et al., "Novel CMOS-Compatible Ultralow Capacitance Hybrid III-V/Si Photodetectors Tested up to 32 Gbps NRZ," in Optical Fiber Communication Conference (OFC) 2019, Th3B.3.

- [4] R. Chen et al., "Nanophotonic integrated circuits from nanoresonators grown on silicon," Nat. Commun., vol. 5, no. 4325, 2014.

- [5] A. Brenneis et al., "Photocurrents in a Single InAs Nanowire/Silicon Heterojunction," ACS Nano, vol. 9, no. 10, pp. 9849–9858, 2015.

- [6] D. Li et al., "Ultra-fast photodetectors based on high-mobility indium gallium antimonide nanowires," Nat. Commun., vol. 10, no. 1664, 2019.

- [7] M. Borg et al., "Vertical III-V nanowire device integration on Si(100)," Nano Lett., vol. 14, no. 4, pp. 1914–1920, 2014.

- [8] D. Cutaia, K. E. Moselund, H. Schmid, M. Borg, A. Olziersky, and H. Riel, "Complementary III-V heterojunction lateral NW Tunnel FET technology on Si," 2016 IEEE Symposium on VLSI Technology, pp. 1–2, 2016.

- [9] M. Borg et al., "High-Mobility GaSb Nanostructures Cointegrated with InAs on Si," ACS Nano, vol. 11, no. 3, pp. 2554–2560, 2017.

- [10] "Synopsys SentaurusTM Device & Electromagnetic Wave Solver (EMW)." Version O-2018.06, 2018.