# **Experimental Demonstration of PAM-4 Transmission** through Microring Silicon Photonic Clos Switch Fabric

Liang Yuan Dai <sup>1</sup>, Yu-Han Hung<sup>1,\*</sup>, Qixiang Cheng<sup>1</sup> and Keren Bergman<sup>1</sup>

Department of Electrical Engineering, Columbia University, New York, NY,10027, USA

\*yh3128@columbia.edu

**Abstract:** We present the first experimental demonstration of a 25 Gbps optical PAM4 signal transmission through a microring-based Clos topology under realistic operating conditions. We observe a 1.1-dBm power penalty at the bit error rate of  $1.03 \times 10^{-7}$ . © 2020 The Author(s) **OCIS codes:** (130.4815) Optical switching devices; (070.6110) Spatial filtering; (230.5750) Resonators;

#### 1. Introduction

Data traffic and energy consumption are two important issues for the current datacenters and high-performance computing systems. For example, the net traffic will be 20.6 zettabytes by 2021, where 73% of workloads stays within the datacenter [1]. To manage the huge data transmission in an efficient way, four-level pulse amplitude modulation (PAM4) signaling in photonic switched interconnects, which possesses the combination of high spectral efficiency, low cost, and low power consumption, has been considered as an effective solution while multi-state coherent links still remain relatively expensive for datacenters [2]. However, comparing with NRZ signaling, PAM4 signaling is more noise-sensitive due to the lower signal-to-noise ratio [3]. The overall link performance of PAM4 transmission can be affected by the nonlinear effects in the photonic switched interconnects. Examining the transmission linearity of photonic switch architectures is therefore of great significance for PAM4 signaling.

As an emergent technology, photonic switch architectures are being researched extensively. Commonly explored topologies include crossbar, Beneš, switch-and-select (S&S), and path-independent-loss (PILOSS) due to their nonblocking characteristics [1]. In the majority of these designs, Mach-Zehnder interferometers (MZIs) have been used as the primary switching element [4]. However, in recent years, microring resonators (MRRs) have shown to be a suitable alternative to MZIs; MRRs' ultra-compact nature, low power consumption, and wavelength selectivity are desirable traits when considering the deployment of high-speed WDM interconnects [5]. Microring optical switch implementations have been demonstrated at low port counts, such as the 8x7 crosspoint, 4x4 hitless, 8x8 Omega, and 4x4 switch-and-select architectures [1]. To exceed beyond the single-digit port radix, we proposed a microringbased Clos switch fabric constructed with switch-and-select switching stages [6]. In this work, we experimentally analyze the performance of a 16x16 microring Clos switch topology under practical operating conditions for datacenter applications, thus sending a 12.5 Gbaud (25 Gbps) PAM4 signal through the network. Here, we observe a 1.1 dB maximum power penalty at a bit error rate (BER) of  $1.03 \times 10^{-7}$ . In contrast with the recently published results on microring switch fabrics [6], our implementation features the highest port count while exhibiting half the power penalty of [5]. The perceived impact of our Clos topology on signal quality is diminished further after considering that optical PAM4 signals carry an intrinsic power penalty of 4.8 dB over OOK-NRZ at the same baud rate [3]. We highlight the results of this experiment as a realistic representation of the near-transparent impact the microring-based Clos switch would have on an optically switched datacenter network.

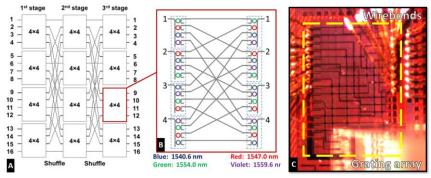

Fig 1: (A) General layout of a 16x16 Clos network. (B) 4x4 microring switch-and-select network. (C) Microscopic image of 4x4 S&S network.

### 2. Switch-Stage Characteristics

In our experiment, we configure a single 4x4 microring S&S stage to emulate the performance of a rearrangeable non-blocking (RNB) 16x16 Clos network. The switch-stage itself, seen in Fig. 1(B), comprises of 32 add-drop ring resonators, each designed to have an optical bandwidth of 76.3 GHz in the C-band. The rings are thermally tunable

M1H.3.pdf OFC 2020 © OSA 2020

through integrated microheaters to a range of 25.4 nm, equal to approximately 1 free spectral range. The through ports of cascaded resonators are connected to output grating couplers, for chip debugging and ring characterization purposes. Individual rings within a cascade resonate on a different wavelength, at 1540.5 nm, 1547.0 nm, 1554.0 nm, and 1559.6 nm. This property can be levied for future WDM experiments; however, it does not affect the scope of the current work. The center shuffle of the switching stage is enabled through silicon waveguide crossings, each determined to be an additional 0.12 dB in on-chip loss. The total on-chip loss through a switch-stage pass is measured to be between 1.8 dB and 2.52 dB, depending on the signal path.

The 4x4 switch-and-select network was taped out via the AIM Photonics Multi-Project Wafer (MPW) run, using foundry specific PDK elements. The entire MPW chip measured in at 8.5 mm x 5 mm, but the switch itself has a compact footprint of 1.2 mm x 1.8 mm. The 34 electrical IOs used for thermal wavelength tuning are wire-bonded to a custom electrical package by Tyndall National Institute. Optical coupling is achieved through an 18-port grating fiber array, attached to the chip by PLC Connections using an UV cured epoxy. A pair of on-chip grating loopback have been included to facilitate the coupling process, which also allows us to assess an optical coupling loss of 4.12 dB per facet. The microscope image of the packaged device can be seen in Fig. 1(C).

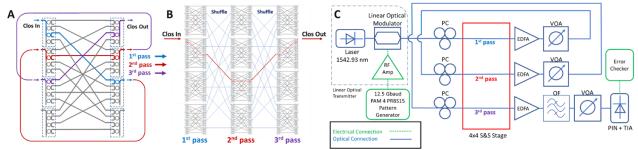

Fig 2: (A) Simplified schematic of switch-stage configuration. (B) The emulated optical path of a Clos network. (C) Full experimental setup.

#### 3. Fabric-Level Evaluation

To emulate the performance of an RNB 16x16 Clos switch fabric, the inputs and outputs of a single 4x4 microring S&S structure are connected in the manner shown in Fig. 2(A). Each ring within the signal path is thermally tuned to resonate at 1542.93 nm. By doing so, we effectively guide a signal through the three switching stages of a Clos network, as seen in Fig. 2(B). The optical path chosen in our configuration represents the average switch route through this architecture, with a mean of 4 waveguide crossings per switch-stage.

Looping the optical signal through the same switching stage provides the benefit of introducing crosstalk into the system; signals on their first pass behave as sources of crosstalk to signals on their second and third pass, and vice versa. Since we are interested in evaluating the behavior of the Clos topology under realistic operating conditions, these crosstalk sources are desirable because they mimic the possible load on optical switches within datacenters, where more than one signal is being routed at a time.

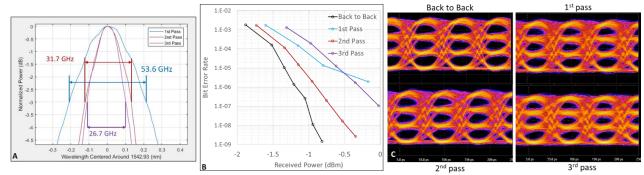

With every pass through the switch-and-select stage, the bandwidth of the optical signal is narrowed by two microring filters. We investigate this effect by injecting an Erbium-doped fiber amplifier (EDFA)-based broadband source through the designated signal path and capturing the optical spectrum after every switch-stage. The results are presented in Fig. 3(A). It can be seen that the optical bandwidth decreases from 53.6 GHz after the first stage to 31.7 GHz after the second, and finally to 26.7 GHz after the third. This narrow-down trend closely follows the approximation described in [6] of:

$$\Delta \lambda_{3dB,k} \approx \Delta \lambda_{3dB} \times \sqrt{2^{\frac{1}{k}} - 1} \tag{1}$$

where *k* is equal to the number of ring filters along the optical path. The reduction to 26.7 GHz after the third pass limits our transmission rate of the signal to around 12.5 Gbaud.

We now move on the full experimental setup, as laid out in Fig. 2(C). An electrical pseudo-random bit sequence (PRBS) PAM4 signal at 12.5 Gbaud is sent to a linear optical transmitter, composed of a tunable laser operating at 1542.93 nm and a 35 GHz Mach-Zehnder modulator. The intensity modulated optical signal (at 6 dBm) is inserted into the first pass of the 4x4 S&S stage, via a polarization controller (PC) tuned to the TE polarization. The output of the first pass is boosted by an EDFA to compensate for grating coupling loss, then attenuated by a variable optical attenuator (VOA) to 2.58 dBm to account for on-chip and inter-stage shuffle loss. The signal is routed through another PC and into the second pass of the switch. Similarly, the output of the second pass is connected to an EDFA and VOA, this time attenuating the signal to 0.12 dBm before it is sent via the PC into the third pass of the switch. The output of the third stage is amplified by a third EDFA, then filtered using an optical bandpass filter (OF) to reduce amplified

M1H.3.pdf OFC 2020 @ OSA 2020

spontaneous emission (ASE) noise from the amplification processes. The optical signal is attenuated by a final VOA before being converted to an electrical signal via a 33 GHz PIN-TIA, where it is lastly analyzed by an error counter. To visualize the transformation of the PAM4 signal as it progresses through the optical path, intermediary data is taken at the output of pass 1 and pass 2 by connecting them directly to the final EDFA-OF-VOA-PIN setup. Fig. 3 (B) and (C) illustrate the results obtained from this experiment, featuring the bit-error ratio (BER) curves taken after each pass of the S&S switch-stage along with the eye diagrams.

Fig 3: (A) Optical path bandpass characterization. (B) BER curves for every signal pass and (C) accompany PAM4 eye diagrams

From the BER curves, we observe a maximum power penalty of 1.1 dB at a bit error rate of  $1.03 \times 10^{-7}$  after three traversals through the S&S stage. The decreased gradient of the BER curve for the 3<sup>rd</sup> pass in comparison with the back-to-back indicates that the signal is encountering intersymbol interference. In addition, the BER waterfall curves show that the power penalty of the 2<sup>nd</sup> pass is consistently half that of the 1<sup>st</sup> pass. Both of these observations can be attributed to the filtering effects of the microring paths [7]. With a passband of 53.6 GHz, the 1<sup>st</sup> pass envelopes a considerate portion of higher-order noise, notably the ASE from the EDFAs, which contributes to a higher bit-error ratio. Conversely, the 3<sup>rd</sup> pass has a passband which is too narrow, and thus not encompassing enough of the optical PAM4 spectrum. The temporal effect of this is the PAM4 signal delaying-and-adding onto itself, akin to how lowpass filters convert NRZ signals into duobinary signals, resulting in intersymbol interference. Lastly, the passband of the 2<sup>nd</sup> pass is around an optimal point; narrow enough to filter out the ASE accumulated through multiple stages of EDFAs, but still wide enough encompass the PAM4 spectrum.

Future implementations of the microring 16 x 16 Clos topology can be improved upon by increasing the passband of the 3<sup>rd</sup> pass to approximately 31.7 GHz, or increasing individual ring resonators to exhibit a passband of 90.7 GHz, as per Equation (1). Doing so may bring the performance of the switch fabric close to the results of the 2<sup>nd</sup> pass, with a power penalty of 0.3 dB at  $1.03 \times 10^{-7}$ . A monolithically integrated Clos network is expected surpass the performance of the current implementation, as it would not need the cascading stages of EDFAs which degrading the optical signal with ASE.

## 4. Conclusion

We present the first experimental analysis of a 25 Gbps optical PAM4 signal traversing through a 16x16 microring Clos topology, which is emulated by configuring the IOs of a single 4x4 switch-and-select stage. Realistic operating conditions for datacenter applications are replicated by introducing crosstalk to the system, representing the possible load on optical switches where more than one signal is being routed at a time. We observe a 1.1 dB maximum power penalty at a BER of  $1.03 \times 10^{-7}$ , with the possibility of reducing it to 0.3 dB if the passbands of resonator switching elements are optimized. The low power penalty of this Clos topology along with its inherent scalability make it suitable candidate for enabling optical interconnectivity between processing nodes within the datacenter architecture.

#### 5. References

- [1] Q. Cheng, et al., "Recent advances in optical technologies for data centers: a review," Optica 5, 1354-1370 (2018)

- [2] E. El-Fiky, et al., "168-Gb/s Single Carrier PAM4 Transmission for Intra-Data Center Optical Interconnects," in IEEE Photonics Technology Letters, vol. 29, no. 3, pp. 314-317, 1 Feb.1, 2017.

- [3] T. Lengyel, et al., "Impact of Damping on 50 Gbps 4-PAM Modulation of 25G Class VCSELs," in Journal of Lightwave Technology, vol. 35, no. 19, pp. 4203-4209, 1 Oct.1, 2017.

- [4] Long Chen, *et al.*, "Compact, low-loss and low-power 8×8 broadband silicon optical switch," Opt. Express 20, 18977-18985 (2012) [5] Y. Huang, *et al.*, "Dual-Microring Resonator Based 8×8 Silicon Photonic Switch," in Optical Fiber Communication Conference (OFC) 2019, OSA Technical Digest (Optical Society of America, 2019), paper W1E.6.

- [6] Q. Cheng, et al., "Scalable Microring-Based Silicon Clos Switch Fabric With Switch-and-Select Stages," in IEEE Journal of Selected Topics in Quantum Electronics, vol. 25, no. 5, pp. 1-11, Sept.-Oct. 2019

- [7] Y. Hung, et al., "Silicon photonic switch-based optical equalization for mitigating pulsewidth distortion," Opt. Express, 27(14), 19426–19435 (2019).