# VCSEL-Based Ultra-Compact Optical Transceiver for Co-Packaged Optics

### Hideyuki Nasu

Photonics Laboratory, Furukawa Electric Co., Ltd., hideyuki.nasu@furukawaelectric.com

**Abstract** This paper introduces a VCSEL-based ultra-compact optical transceiver using multi-core fibres for Co-Packaged Optics under development in the NICT B5G BRIGHTEN project, which is targeting a very high bandwidth density of 13.3 Gbps/mm<sup>2</sup>. A CPO daughter board and a network switch server are also introduced. ©2023 The Author(s)

### Introduction

Co-Packaged Optics (CPO) has been expected to expand the bandwidth and save the link power in data centre interconnects (DCIs). In particular, low power density, expressed with energy-per-bit, has been demanded since there is a concern that the link power will be increased 26 times as expanding the bandwidth of network switch ASIC from 640 Gbps to 51.2 Tbps [1].

S. Fathololoumi et al. demonstrated a 106.25-Gbps × 8-channel Mach-Zehnder modulator (MZM)-based Silicon Photonics (SiPh) transceiver with a power density of 19.3 pJ/bit where the integrated laser source consumed 3.9 pJ/bit [2]. M. Wade demonstrated an  $8-\lambda \times 16$ -Gbps/ $\lambda \times 16$ -port micro-ring resonator modulator (MRM)-based SiPh transceiver with a power density of 4.96 pJ/bit which does not take account of the power consumed at both heaters integrated to the MRMs and an external laser source [3].

To save the link power, the usage of vertical cavity surface emitting laser (VCSEL)-based optical transceivers are a promising solution by taking advantage of the low current drive characteristics. D. Kuchta reported the ARPA-E MOTION project where a 56 Gbps NRZ × 16-channel optical transceiver was demonstrated with a very low power density of 4 pJ/bit in phase 1 and a 112 Gbps PAM4 × 32-channel optical transceiver is under development with an extremely low power density target of 2 pJ/bit [4]. An 850-nm multi-mode (MM) VCSEL exhibited a modulation capability of 56 Gbaud, but the multi-mode fibre (MMF) link distance was limited within 30 m.

The NICT B5G BRIGHTEN project has launched since 2021 where a 1060-nm singlemode (SM) VCSEL-based ultra-compact 16channel optical transceiver has been developed with a very high-density optical interface using multi-core fibres (MCFs) [5]. In the first stage, a modulation speed per channel is as high as 25 Gbps NRZ and then it is upgraded to 50 Gbps NRZ and 100 Gbps PAM4 in the second stage, where a power density of <4 pJ/bit has been targeted.

In this paper, the 25-Gbps NRZ × 16-channel ultra-compact optical transceiver and an electrical pluggable interface using 0.3-mm pitch land grid array (LGA) are described [6]. A testing station for the ultra-compact transceiver is also demonstrated where its practicality was verified with an 850-nm multi-mode (MM) VCSEL-based 56-Gbps PAM4 × 8-channel optical transceiver whose electrical interface is compliant with the 25-Gbps NRZ  $\times$  16-channel transceiver [7]. By adopting an integrated electrical pluggable interface to accommodate 8 optical transceivers, a CPO daughter board which accommodates 32 transceivers was fabricated [8]. We also fabricated a network switch server which accommodates 4 CPO daughter boards.

### Ultra-compact 16-channel CPO transceiver

Fig. 1 shows a schematic illustration for a cross-sectional structure of the ultra-compact 16-channel CPO transceiver using MCFs and a bottom-emitting coupled-cavity 1060-nm SM InGaAs/GaAs VCSEL array [9]. By adopting spatial division multiplexing (SDM) using 16 cores of an SM 19-core fibre, the transmission capacity per fibre is expanded 16 times. Laser beams launched from the VCSEL array with a wavelength of 1060 nm are transmitted through the substrate. To realize butt-coupling between the VCSEL array and the MCF, the mode field diameter (MFD) is reduced to ~6 µm by increasing the refractive index difference between the core and the cladding of the MCF, and the MFD of the VCSEL is expanded to ~6 µm by using a coupled-cavity structure. The 16channnel VCSEL array is flip-chip-bonded on a top surface of an organic interposer together with a photo diode (PD) array. A VCSEL driver (VD) and a transimpedance amplifier (TIA) are also flip-chip-bonded on the bottom surface of the interposer. Hence, parasitic components of the electrical wiring are significantly suppressed, and accordingly it contributes to realize high-

Electrical pluggable interface

**Fig. 1:** Schematic illustration for a cross-sectional structure of the ultra-compact 16-channel CPO transceiver.

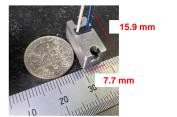

Fig. 2: Photograph of the 25-Gbps  $NRZ \times 16$ -channel ultracompact optical transceiver.

speed operations. By realizing the direct optical coupling between the VCSEL array and the SMthe CPO transceiver enables MCF, а transmission distance of >2 km, which is required for DCIs. A heat dissipation structure is adopted to the bottom side of transceiver since the heat is mostly generated the VD and TIA mounted on the bottom surface of the interposer. This structure requires making an enough heat dissipation area on the footprint. A 0.3-mm pitch LGA is adopted to minimize the electrical interface and hence it contributes to make an enough space for the heat dissipation. The mechanical size is as small as 15.9 mm (length) × 7.7 mm (width) × 7.95 mm (height). The modulation speed per channel will be upgraded to 100 Gbps and hence it will realize a very high bandwidth density of 13.3 Gbps/mm<sup>2</sup>.

# Electrical pluggable interface and testing station

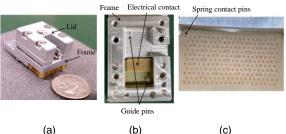

A land grid array (LGA) interface is employed for the electrical interface, and its size can be determined by the number of lands and a pitch size. Electrical contact pins are used to connect between a CPO transceiver and a daughter board. Optical Internetworking Forum (OIF) issued an implementation agreement for a 3.2-Tbps CPO module whose footprint is as large as 32.6 mm x 21.0 mm with a 0.6-mm pitch LGA [10]. To decrease the mechanical size of a transceiver, it is much preferable to use a highdensity electrical interface. In addition, the number of ground lands surrounding high-speed lands can be reduced by adopting a staggered pad arrangement, row by row. Fig. 3 (a) shows a photograph of the electrical pluggable interface

**Fig. 3:** Photographs of an electrical pluggable interface. (a) Appearance. (b) Inner socket. (c) Spring contact pins with a staggered arrangement.

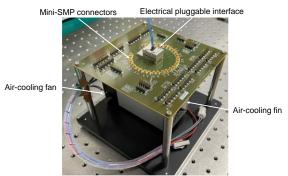

**Fig. 4:** Photograph of a testing station using the electrical pluggable interface.

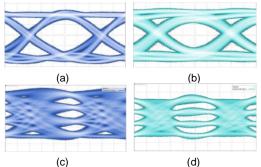

Fig. 5: TX and RX eye diagrams. (a) 28 Gbps NRZ for TX. (b) 28 Gbps NRZ for RX. (c) 56 Gbps PAM4 for TX. (d) 56 Gbps PAM4 for RX.

using a 0.3-mm-pitch LGA, together with a US 10-cent coin for size comparison. The 0.3-mm pitch LGA contributes to realize the small footprint of 15.9 mm × 7.7 mm. The transceiver can be attached to a socket which realizes precise mechanical alignment between the LGA and the spring pins. A lid is attached to the frame and provide an appropriate mechanical force to the transceiver in order to realize good electrical contacts. Fig. 3 (b) shows the inner socket to insert the transceiver to the electrical pluggable interface. The transceivers are precisely aligned by guide pins and electrically connected by spring contact pins. Fig. 3 (c) shows the spring contact pins with a staggered arrangement. A 3-dB bandwidth of the pluggable interface is >40 GHz. Fig. 4 shows a testing station using the electrical pluggable interface. A 3-dB bandwidth for the test board including the electrical pluggable interface is >17.3 GHz. In order to characterize the electrical pluggable interface and the testing station, an 850-nm MM VCSEL-based 56-Gb/s PAM4 × 8-channel optical transceiver [7] was attached to the electrical interface. As shown in Fig. 5 (a), the 28-Gbps NRZ eye diagrams of the transmitter (TX) and receiver (RX) output signals exhibit clear eye opening. It evidently shows that electrical transmission lines on the test board have wide enough bandwidths. Fig. 5 (b) shows the eye diagrams operated with a 56-Gb/s PAM4 signal where the CDR functionality for both TX and RX was activated. The eye diagram of the TX and the RX output signals show clear eye opening and hence this testing station can be employed for the characterization of both 28-Gbaud NRZ and PAM4 optical transceivers.

# CPO daughter board and network switch server

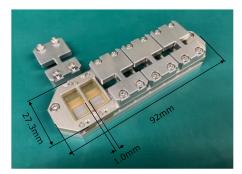

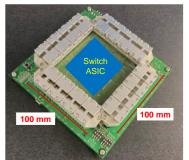

We also fabricated an integrated electrical pluggable interface to accommodate 8 optical transceivers. Fig. 6 shows a photograph of an integrated electrical pluggable interface for 8 transceivers. The optical transceivers can be accommodated with a clearance of 1 mm by inserting it into an individual socket and hence the total width of the integrated electrical pluggable interface is as short as 92.0 mm. The integrated electrical pluggable interface uses the 0.3-mm pitch LGA and spring pins with the staggered pad arrangement as well. A lid is prepared for 2 transceivers, and it can provide an appropriate mechanical force to realize good electrical contacts. The lid has windows to pass through the pigtailed MCF cables. Fig. 7 shows a photograph of a CPO daughter board with the integrated electrical pluggable interfaces where a switch ASIC is mounted on the centre of the CPO board. The size of daughter board is as small as 100 mm  $\times$  100 mm. At the four edges of daughter board, the integrated electrical pluggable interface is attached. Hence, the CPO daughter board can accommodate 32 transceivers. The CPO transceivers have the pigtailed MCF cables perpendicular to the electrical interface. Since the optical interfaces do not interfere even if the CPO daughter boards are brought close to each other, it is possible to install multiple daughter boards in one server. We fabricated a switch server accommodating 4 CPO daughter boards whose photograph is shown in Fig. 8.

### Conclusion

The NICT B5G BRIGHTEN project has been developing an ultra-compact 16-channel optical transceiver using MCFs and a bottom-emitting

**Fig. 6:** Photograph of an integrated electrical pluggable interface for 8 optical transceivers.

**Fig. 7:** Photograph of a CPO daughter board with the integrated electrical pluggable interfaces.

Fig. 8: Photograph of a switch server accommodating 4 CPO daughter boards.

coupled-cavity 1060-nm SM InGaAs/GaAs VCSEL array. The modulation speed per channel is as high as 25 Gbps NRZ in the first stage and then it is upgraded to 50 Gbps NRZ and 100 Gbps PAM4 in the second stage. A very high bandwidth density of 13.3 Gbps/mm<sup>2</sup> will be realized. The electrical pluggable interface using 0.3-mm pitch LGA and the testing station for the ultra-compact optical transceiver were demonstrated. The CPO daughter boards to accommodate 32 CPO optical transceivers and the network switch server to accommodate 4 CPO daughter boards were introduced.

## Acknowledgement

These research results were obtained from the commissioned research (#00101) by National Institute of Information and Communications Technology (NICT), Japan.

#### References

- R. Chopra, "Solving the Power Challenge," TEF2021 Keynote, Feb. 2021. [online] Available: https://ethernetalliance.org/blog/2021/02/24/lookingbeyond-400g-a-system-vendor-perspective/

- [2] S. Fathololoumi, D. Hui, S. Jadhav, J. Chen, K. Nguyen, M.N. Sakib, Z. Li, H. Mahalingam, S. Amiralizadeh, N. N. Tang, H. Potluri, M. Montazeri, H.Frish, R. A. Defrees, C. Seibert, A. Krichevsky, J. K. Doylend, J. Heck, R. Venables, A. Dahal, A. Awujoola, A. Vardapetyan, G. Kaur, M. Cen, V. Kulkarni, S. S. Islam, R. L. Spreitzer, S. Garag, A. C. Alduino, RK Chiou, L. Kamyab, S. Gupta, B. Xie, R. S. Appleton, S. Hollingsworth, S. McCargar, Y. Akulova, K. M. Brown, R. Jones, D. Zhu, T. Liljeberg, and L. Liao: "1.6 Tbps Silicon Photonics Integrated Circuit and 800 Gbps Photonic Engine for Switch Co-Packaging Demonstration," Journal of Lightwave Technology, Vol.39, No.4 pp.1155-1161, Feb. 2021.

- [3] M. Wade, E. Anderson, S. Ardalan, W. Bae, B. Beheshtian, S. Buchbinder, K. Chang, P. Chao, H. Eachempatti, J. Frey, E. Jan, A. Katzin, A. Khilo, D. Kita, U. Krishnamoorthy, C. Li, H. Lu, F. Luna, C. Madden, L. Okada, M. Patel, C. Ramamurthy, M. Raval, R. Roucka, K. Robberson, M. Rust, D. Van Orden, R. Zeng, M. Zhang, V. Stojanovic, F. Sedgwick, R. Meade, N. Chan, J. Fini, B. Kim, S. Liu, C. Zhang, D. Jeong, P. Bhargava, M. Sysak, C. Sun: "An Error-free 1 Tbps WDM Optical I/O Chiplet and Multi-wavelength Multi-port Laser," OFC2021, F3C.6, Mar. 2021.

- [4] D. Kuchta, "Co-Packaging on Organic Laminates: MOTION Phase 2," ARPA-E ENLITENED Kickoff Meeting, Jan. 2021. [online] Available: https://arpae.energy.gov/sites/default/files/2021-01/DAY1\_Kuchta\_ENLITENED%20Kickoff.pdf

- [5] T. Yagisawa, M. Miyoshi, J. Miike, T. Azuma, Y. Harada, S. Ide, and K. Morito, "Novel Packaging Structure Using VCSEL Array and Multi-Core Fiber for Co-Packaged Optics," ICSJ2022, 01-03. Nov. 2022.

- [6] Y. Ishige, K. Nagashima, W. Yoshida, and H. Nasu, "Testing station using a 0.3-mm-pitch LGA interface for a 25-Gbaud x 16-channel CPO transceiver," ICSJ2022, 01-02, Nov. 2022.

- [7] W. Yoshida, Y. Ishige, K. Nagashima, and H. Nasu, "56-Gb/s PAM4 x 8-Channel VCSEL-Based Optical Transceiver for Co-Packaged Optics," ICSJ2022, 01-01, Nov. 2022.

- [8] K. Takahashi, K. Miura, H. Nakajima, N. Soya, S. Torimitsu, Y. Ishige, K. Nagashima, H. Nasu, and S. Fukutomi, "Design of CPO Daughter Board with FPGA and 25-Gbaud x 16-Channel Ultra-Compact Optical Transceivers," ICSJ2022, 01-04, Nov. 2022.

- [9] L. Dong, X. Gu and F. Koyama, "16-ch 1060-nm Singlemode Bottom-emitting Metal-aperture VCSEL Array for Co-packaged Optics," OFC2023, W4B.3, Mar. 2023.

- [10] Optical Internetworking Forum, "Implementation Agreement for a 3.2Tb/s Co-Packaged (CPO) Module," OIF-Co-Packaging-3.2T-Module-01.0, Mar. 2023.