# Experimental Study of the Equalization Requirements of a 2.5D Co-Packaged 16-nm CMOS Optical Receiver up to 160 Gb/s

Tu5.26

Dhruv Patel<sup>(1)</sup>, Bahaa Radi<sup>(1)</sup>, Alireza Sharif-Bakhtiar<sup>(2, now with 3)</sup>, Anthony Chan Carusone<sup>(1, 3)</sup>

<sup>(1)</sup> Department of Electrical and Computer Engineering, University of Toronto, 10 King's College Rd, Toronto, Ontario, M5S3G4, Canada, dhruv.patel@isl.utoronto.ca

<sup>(2)</sup> Huawei Technologies Canada, 19 Allstate Pkwy, Markham, Ontario, L3R5A4, Canada

<sup>(3)</sup> Alphawave IP, 70 University Ave, Toronto, Ontario, M5J2M4, Canada

**Abstract** We demonstrate the DSP-based feed-forward and decision-feedback equalization requirements in 2.5D co-packaged CMOS optical receivers. Experimental results confirm optical reception up to 160-Gb/s/ $\lambda$  PAM-4 and 90-Gb/s/ $\lambda$  NRZ signaling with a bandwidth-limited prototype comprised of a TIA in 16-nm FinFET CMOS co-packaged with a commercial photodiode. ©2022 The Author(s)

## Introduction

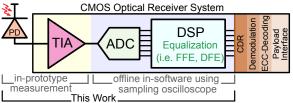

Ethernet standards, such as PAM-4 800G-DR8 and 400G-DR4/FR4 for intra-data center links with intensity-modulation direct-detection (IM/DD) systems, require the design of energy-efficient and low-cost optical receivers supporting data rates exceeding 100 Gb/s/ $\lambda^{[1],[2]}$ . While SiGe BiC-MOS technologies offer high gain and low noise optical receivers<sup>[3],[4]</sup>, advanced CMOS technologies allow the integration between the optical receivers and the host SerDes on the same chip while offering good switching characteristics with high energy efficiency<sup>[5]</sup>. This can be leveraged in the design of low-cost and high-density receivers that use equalization implemented in digital-signal-processing (DSP) to achieve higher data rates<sup>[6],[7]</sup>. Such optical receiver comprising a transimpedance amplifier (TIA) followed by ADC and DSP are shown in Fig. 1.

Traditional optical receivers with TIA in the front-end are designed to have bandwidths (BWs) in the range of  $0.5-0.7\times$  of baud rate. However, at data rates exceeding 150 Gb/s, achieving the required BW comes with the cost of heavily reduced transimpedance. This leads to degraded sensitivity, higher thermal noise, and higher power<sup>[8]</sup>. To overcome this trade-off, the TIA BW can be intentionally limited to below  $0.5\times$  baud rate, allowing for increased transimpedance at the cost of the intersymbol interference (ISI)<sup>[9]</sup>. ISI can then be removed with widely adapted, DSP-compatible, and CMOS suitable equalization techniques that are the feed-forward equality of the transimple of the techniques that are the feed-forward equality of the technique techniques that are the feed-forward equality of the technique techniques that are techniques techni

Fig. 1: Block diagram of a CMOS optical receiver system.

izer (FFE) and the decision feedback equalizer (DFE)<sup>[10]</sup>. Several state-of-the-art CMOS optical receivers<sup>[11],[12]</sup> have used such approach but the equalization taps were limited to a few. Many recent works have also demonstrated 100+Gb/s with sophisticated DSP approaches which can entail much higher silicon area and power<sup>[13]–[15]</sup>. However, the study of DSP requirements and its full potential with simple equalization strategies such as FFE and DFE are not yet clear<sup>[16]</sup>, especially in co-packaged CMOS optical receiver system performing at such high data rates.

For higher data rate operation with a limited-BW receiver, it is crucial to appropriately select the number and the combinations of FFE (i.e. precursors and post-cursors) and DFE taps. This work, demonstrates up to 160 Gb/s PAM-4 optical data reception with a co-packaged CMOS optical receiver with a limited BW of 32 GHz while reporting the DSP-based FFE and DFE equalization requirements.

## **Simulated Equalization Requirements**

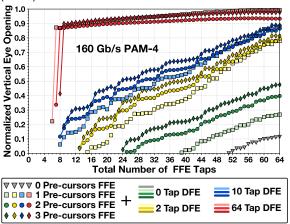

To highlight the FFE/DFE requirements at such datarates, we study the vertical-eye-opening (VEO) across various combinations of FFE and

Fig. 2: Simulated VEO as a function of the total number for FFE taps across various combinations of FFE pre-cursor taps and DFE taps at 160 Gb/s PAM-4.

Tu5.26

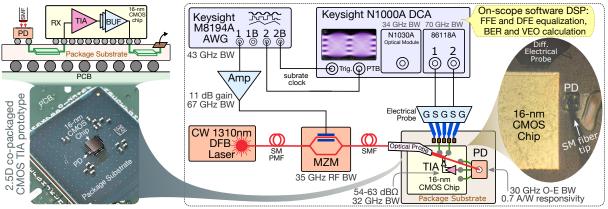

Fig. 3: Measurement setup to study the FFE/DFE equalization requirements in 2.5D co-packaged CMOS optical receivers.

DFE taps. Fig.2 shows the simulated worst-case VEO as a function of total number of FFE taps across various combinations of pre-cursor FFE taps and DFE taps at 160 Gb/s PAM-4. Worstcase VEO is computed using peak-distortion analysis<sup>[17]</sup> after processing the pulse response through in-software FFE/DFE with optimized tap coefficients. The pulse response is obtained from the measured transimpedance response from our recent work<sup>[18]</sup>. As can be seen with the case of 0 tap DFE, having more pre-cursor FFE taps leads to significantly improved VEO with diminishing return after 2 pre-cursor taps. Moreover, adding more DFE taps for a given number of FFE taps always leads to improved VEO. We further demonstrate this study with measurements.

## **Experimental Setup**

Fig .3 shows the optoelectrical measurement setup. A lensed single-mode fiber tip is used

to free-space couple the modulated optical signal ( $\lambda$ =1310 nm) onto the back-illuminated PD (30 GHz O-E BW and 0.7 A/W responsivity) with flipchip 2.5D co-packaged 16-nm FinFET CMOS TIA prototype with 32 GHz BW described in our recent work<sup>[18]</sup>. Differential TIA outputs are electrically probed and captured by a sampling oscilloscope which performs the desired FFE and DFE equalization with optimum tap coefficients mimicking the ADC and DSP blocks from Fig. 1.

## **Experimental Results and Discussions**

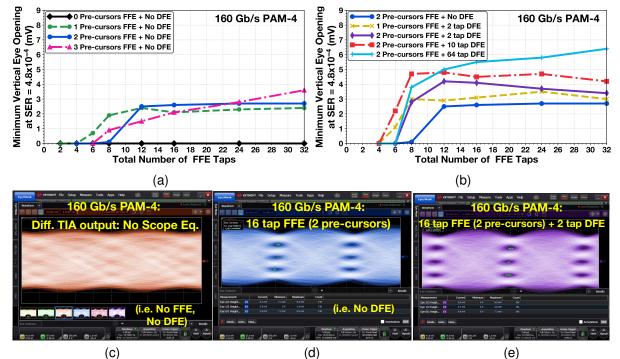

160 Gb/s PAM-4 measurements are performed with QPRBS13 pattern with input optical modulation amplitude (OMA) of -4.24 dBm, extinction ratio (ER) of 1.26 dB, and TIA gain set at 60 dB $\Omega$ . Minimum VEO at symbol-error-rate (SER) of  $4.8 \times 10^{-4}$  (pre-FEC limit<sup>[1]</sup>) is measured. Fig .4a shows the resulting VEO across the total number of FFE taps for a different number of pre-

Fig. 4: Measured VEO at 160 Gb/s PAM-4 with (a) FFE only (b) FFE + DFE. Eye diagrams of (c) TIA output without FFE or DFE (d) with 16 tap FFE (2 pre-cursor) (e) with 16 tap FFE (2 pre-cursor) + 2 tap DFE.

Tu5.26

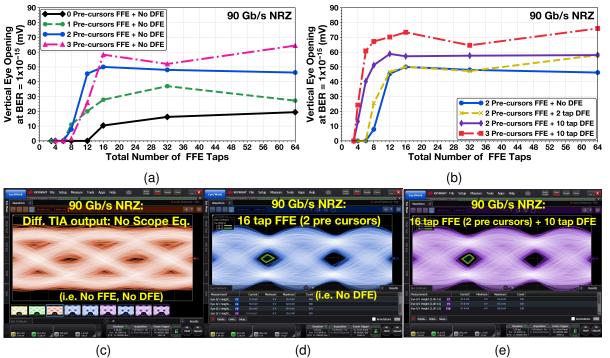

Fig. 5: Measured VEO at 90 Gb/s NRZ with: (a) FFE only (b) combinations of FFE + DFE. Measured eye diagrams of: (c) TIA output without equalization (no FFE/DFE) (d) with 16 tap FFE (2 pre-cursors) (e) with 16 tap FFE (2 pre-cursors) + 10 tap DFE.

cursors. Measurements reveal that at least one pre-cursor tap is required to open the eye (i.e., VEO>0) with diminishing return after 2 pre-cursor FFE taps. Fig.4b shows the VEO when DFE is enabled along with FFE. It clearly emphasizes that having more DFE taps further improves the VEO, albeit with a diminishing improvement for DFE taps greater than 10 taps. Resulting eye diagrams of the prototype outputs without any equalization is shown in Fig.4c followed by the DSP processed eye-diagrams after enabling total of 16 tap FFE (2 pre-cursor taps) with no DFE and 16 tap FFE (2 pre-cursor taps) + 2 tap DFE illustrated in Fig. 4d, and Fig.4e, respectively.

Experiment is further performed for 90 Gb/s NRZ with required bit-error-rate (BER)< $1 \times 10^{-15}$  targeted for low-latency optical receivers (i.e. no forward-error-correction is tolerable). Measurements are executed with a PRBS11 pattern with -4.37 dBm input OMA, 1.25 dB ER and 63 dB $\Omega$  gain in TIA. As shown in Fig. 5a, for a given number of FFE taps, as the number of pre-cursor taps is increased, VEO is improved; again with the diminishing return for pre-cursor taps greater than 2. Moreover, adding DFE taps further improves VEO as shown in Fig.5b. To show this trend, captured eye diagrams with three different equalization settings are shown in Fig.5c, 5d and 5e.

Note that the VEO increases sharply with the total number of FFE taps up to roughly 12 taps

since ISI is dominant and additional equalization significantly improves VEO. As the total number of FFE taps grows beyond 12 taps, all possible improvement from equalizing BW limitations and reflections has already been achieved so the VEO approaches a relatively constant value. Thermal noise then limits the performance resulting in small variations in measured VEO for total number of FFE taps more than approximately 12 taps.

## Conclusion

We have experimentally demonstrated 160 Gb/s PAM-4 and 90 Gb/s NRZ optical data reception while highlighting the importance of pre-cursor FFE taps, the total number of FFE taps and DFE taps for a 2.5D co-packaged CMOS optical receiver prototype with a limited TIA BW of 32 GHz and a PD BW of 30 GHz. Notably, at least 12 total FFE taps with minimum of 2 precursor taps in combination with 2-to-10 DFE taps were required to achieve near-optimum performance. ADCbased co-packaged CMOS optical receivers can leverage this simple digital equalization approach to achieve data rates required by the 400G/800G and emerging 1.6T Ethernet standards.

#### Acknowledgement

Authors are grateful for funding support from NSERC and technical support from Huawei Technologies Canada.

#### References

- IEEE P802.3df 200 Gb/s, 400 Gb/s, 800 Gb/s, and 1.6 Tb/s Ethernet Task Force, Mar. 2022. [Online]. Available: https://www.ieee802.org/3/df/.

- [2] Common Electrical I/O (CEI)-224G. [Online]. Available: https://www.oiforum.com/technical-work/hottopics/common-electrical-io-cei-224g/.

- [3] S. Voinigescu, T. Dickson, R. Beerkens, I. Khalid, and P. Westergaard, "A comparison of Si CMOS, SiGe BiC-MOS, and InP HBT technologies for high-speed and millimeter-wave ICs", in *Digest of Papers. 2004 Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, 2004.*, 2004, pp. 111–114. DOI: 10.1109/ SMIC.2004.1398180.

- [4] B. Moeneclaey, G. Kanakis, J. Verbrugghe, et al., "A 64 Gb/s PAM-4 linear optical receiver", in 2015 Optical Fiber Communications Conference and Exhibition (OFC), 2015, pp. 1–3. DOI: 10.1364/0FC.2015.M3C.5.

- [5] S. Callender, W. Shin, H.-J. Lee, S. Pellerano, and C. Hull, "FinFET for mm Wave - Technology and Circuit Design Challenges", in 2018 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), 2018, pp. 168–173. DOI: 10.1109/BCICTS.2018.8551125.

- [6] Y. Hong, K. Li, C. Lacava, et al., "Beyond 100-Gb/s Direct-Detection Transmission using an Optical Receiver Co-Integrated with a 28-nm CMOS Gain-Tunable Fully-Differential TIA", in 2020 Optical Fiber Communications Conference and Exhibition (OFC), 2020, pp. 1– 3. DOI: 10.1364/0FC.2020.Th3J.4.

- [7] O. Ishida, K. Takei, and E. Yamazaki, "Power efficient DSP implementation for 100G-and-beyond multi-haul coherent fiber-optic communications", in 2016 Optical Fiber Communications Conference and Exhibition (OFC), 2016, pp. 1–3. DOI: 10.1364/0FC.2016.W3G.3.

- [8] E.Säckinger, "The Transimpedance Limit", IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 57, no. 8, pp. 1848–1856, 2010. DOI: 10.1109/ TCSI.2009.2037847.

- [9] B. Radi, D. Abdelrahman, O. Liboiron-Ladouceur, G. Cowan, and T. C. Carusone, "Optimal Optical Receivers in Nanoscale CMOS: A Tutorial", *IEEE Transactions on Circuits and Systems II: Express Briefs*, pp. 1–1, 2022. DOI: 10.1109/TCSII.2022.3166468.

- [10] X. Tang, Y. Qiao, Y.-W. Chen, Y. Lu, and G.-K. Chang, "Digital Pre- and Post-Equalization for C-Band 112-Gb/s PAM4 Short-Reach Transport Systems", *Journal* of Lightwave Technology, vol. 38, no. 17, pp. 4683– 4690, 2020. DOI: 10.1109/JLT.2020.2993997.

- [11] H. Li, C.-M. Hsu, J. Sharma, J. Jaussi, and G. Balamurugan, "A 100-Gb/s PAM-4 Optical Receiver With 2-Tap FFE and 2-Tap Direct-Feedback DFE in 28-nm CMOS", *IEEE Journal of Solid-State Circuits*, vol. 57, no. 1, pp. 44–53, 2022. DOI: 10.1109 / JSSC.2021. 3110088.

- [12] I. Ozkaya, A. Cevrero, P. A. Francese, et al., "A 64-Gb/s 1.4-pJ/b NRZ Optical Receiver Data-Path in 14-nm CMOS FinFET", IEEE Journal of Solid-State Circuits, vol. 52, no. 12, pp. 3458–3473, 2017. DOI: 10.1109/JSSC.2017.2734913.

- [13] M. S. Bin Hossain, G. Böcherer, T. Rahman, et al., "Experimental Comparison of Cap and Cup Probabilistically Shaped PAM for O-Band IM/DD Transmission System", in 2021 European Conference on Optical Communication (ECOC), 2021, pp. 1–4. DOI: 10.1109 / EC0C52684.2021.9605995.

- [14] L. Xue, L. Yi, W. Hu, R. Lin, and J. Chen, "Optics-Simplified DSP for 50 Gb/s PON Downstream Transmission using 10 Gb/s Optical Devices", *Journal of Lightwave Technology*, vol. 38, no. 3, pp. 583–589, 2020. DOI: 10.1109/JLT.2019.2942438.

- [15] N. Kikuchi and R. Hirai, "Intensity-modulated / directdetection (IM/DD) Nyquist pulse-amplitude modulation (PAM) signaling for 100-Gbit/s/λ optical short-reach transmission", in 2014 The European Conference on Optical Communication (ECOC), 2014, pp. 1–3. DOI: 10.1109/EC0C.2014.6964069.

- [16] A. Stark and T. Detwiler, "Equalization Strategies for 25G PON", in *Optical Fiber Communication Conference*, Optica Publishing Group, 2017, Th2A.24. DOI: 10.1364/0FC.2017.Th2A.24. [Online]. Available: http://opg.optica.org/abstract.cfm?URI=0FC-2017-Th2A.24.

- [17] B. Casper, M. Haycock, and R. Mooney, "An accurate and efficient analysis method for multi-Gb/s chip-to-chip signaling schemes", in 2002 Symposium on VLSI Circuits. Digest of Technical Papers (Cat. No.02CH37302), 2002, pp. 54–57. DOI: 10.1109/VLSIC.2002.1015043.

- [18] D. Patel, A. Sharif-Bakhtiar, and A. Chan Carusone, "A 112 Gb/s -8.2 dBm Sensitivity 4-PAM Linear TIA in 16nm CMOS with Co-Packaged Photodiodes", in 2022 IEEE Custom Integrated Circuits Conference (CICC), 2022, pp. 1–2.