# Impact of Seed Annealing on the Reliability of Monolithic GaAs/Si p-n Diode Optical Phase Shifters

Mo3F.6

Artemisia Tsiara<sup>(1),\*</sup>, Younghyun Kim<sup>(1),(2)</sup>, Didit Yudistira<sup>(1)</sup>, Bernardette Kunert<sup>(1)</sup>, Marina Baryshnikova<sup>(1)</sup>, Marianna Pantouvaki<sup>(1),(3)</sup>, Joris Van Campenhout<sup>(1)</sup>, Kristof Croes<sup>(1)</sup>

<sup>(1)</sup> imec, Kapeldreef 75, 3001 Leuven, Belgium, \*<u>artemisia.tsiara@imec.be</u>

<sup>(2)</sup> Now with Department of Photonics and Nanoelectronics, BK21 FOUR ERICA-ACE Center, Hanyang University, Ansan 15588, Korea

<sup>(3)</sup> Now with Microsoft Research Ltd, 21 Station Road, Cambridge CB1 2FB, United Kingdom

**Abstract** We report the reliability assessment of carrier-depletion p-n diode GaAs/Si optical modulators monolithically integrated on a 300-mm Si wafer. Dark current remains stable under long accelerating aging tests. Devices without seed annealing experience a shift of  $V_{\pi}$ . $L_{\pi}$  with no stress temperature dependence.

# Introduction

Over the past decades, the ongoing demand for optical transceivers has transitioned Silicon Photonics (SiPho) from an early research development [1] to a mature technology [2]. Leveraging its compatibility with the existing complementary metal oxide semiconductor (CMOS) platforms, it enables dense [3] and highyield manufacturing, providing an extended library of components, both on the transmitter and receiver side [4], [5].

Even though the majority of devices are monolithically integrated using Silicon (Si) and Germanium (Ge) on a Si wafer [6], the increasing interest of light generation and amplification [3] paved the way for the integration of III-V direct bandgap materials. Going beyond laser fabrication, features like lower effective mass and higher carrier mobility are making III-V materials more suitable for high-speed electronic devices than bulk Si [7]. Recent works [8]-[10] have demonstrated a highly efficient carrier-depletion optical phase modulator, with direct growth of GaAs on Si, benefiting from the above characteristics.

Besides the many advantages, direct growth of III-V materials on Si comes with a price. Large mismatches in lattice constant and the coefficient of thermal expansion (CTE) between III-V materials and Si are some of the challenges to overcome for a high-quality monolithic integration. Threading dislocations, {111} defects and misfit dislocations formed during process, can significantly impact the dark current of those components, which eventually affects the specifications for the signal-to-noise ratio. Different approaches to reduce the defect density have been established by various groups [11]-[17] with the majority of them being based on high-temperature annealing (600 °C to 1000 °C). An alternative method is to grow the III-V material in trenches with a V-shaped bottom consisting of two {111} facets, a very beneficial approach since no specific high-temperature surface treatment is required [17]. In this paper, we report the impact of seed annealing on the performance and reliability of GaAs/Si V-groove depletion-type modulators.

# **Devices and experiments**

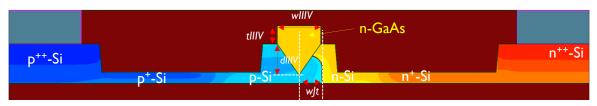

The III-V/Si optical phase shifters were fabricated in imec's 300-mm CMOS pilot line, using a Silicon-On-Insulator (SOI) wafer with a 215 nm top Si layer on a 2 µm thick Buried Oxide. N-type doped GaAs was grown using a two-step Selective-area Epitaxial Growth on V-groove Si trenches, with an optional seed annealing step at 530 °C between them, followed by a p-type and n-type Si implantation to form the near-vertical pn junction. Details on the GaAs growth and all implant conditions can be found in [18] and [10], respectively. Finally, after Chemical Mechanical Polishing, a GaAs thickness of 70-90 nm above the Si rib is reached. A detailed cross-section is shown in Fig. 1 and Tab. 1 describes the different dimensions.

Tab. 1: List of parameters and dimensions used in this work for a 500  $\mu m$ -long device.

| Parameter                                              | Value [nm] |

|--------------------------------------------------------|------------|

| III-V thickness on Si rib ( <i>tIIIV</i> )             | 70~90      |

| III-V width ( <i>wIIIV</i> )                           | 240        |

| III-V depth (dIIIV)                                    | 170        |

| Distance between center to p-n junction ( <i>wJt</i> ) | 100        |

For this study, 500  $\mu$ m-long devices with and without seed annealing have been selected. Package-level accelerating aging tests were with  $T_{\text{stress}}$  conditions of 150 °C, 175 °C and 85 °C/85 % Relative Humidity (RH), biased at  $V_{\text{stress}}$  of -5 V. During these stress conditions, we monitored

Mo3F.6

Fig. 1: Cross-section of the GaAs/Si optical phase shifter.

the dark current shift for up to 5000 h of stress time, while the electro-optical performance of the components was evaluated at room temperature and at different time intervals.

### **Stress results**

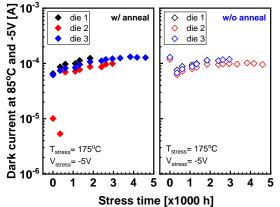

Accelerated aging tests are performed at high temperatures for long stress times, while the stress sequence is interrupted at regular intervals dark electro-optical for current and measurements at lower conditions. Selecting the highest applied  $T_{\text{stress}} = 175 \text{ °C}$  and plotting the dark current at 85 °C and -5 V, it is clear from Fig. 2, that there is no significant impact of the seed annealing step on both the initial dark current and its degradation. Hence, the devices are considered as electrically reliable components.

Fig. 2: Dark current evolution at operating conditions, for stress at 175 °C and -5 V, indicating no impact of seed annealing step.

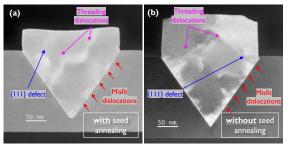

Failure analysis was carried out on two identical stressed samples (175 °C and -5 V for 5000 h), from each process condition, using darkfield scanning transmission electron microscopy (DF-STEM). From the zoomed-in cross-sections shown in Fig. 3, the presence of threading dislocations is evident in the GaAs, while misfit dislocations are appearing at the GaAs/Si interface of the V-groove, as very bright contrast lines. Additionally, {111} defects are highlighted in the figure, but are more clearly detectable in a different imaging condition, the two-beam brightfield (BF) TEM, that is not presented here. Even though the seed annealing step reduces the threading dislocations inside the bulk GaAs, the

Fig. 3: DF-STEM of the GaAs/Si cross-sections on stressed devices (a) with and (b) without seed annealing, both with observable threading dislocations in the GaAs and misfit dislocations at the III-V/Si interface.

fact that  $I_{dark}$  is similar between the two types of components, could be attributed mainly to the contribution of GaAs/Si interface defects.

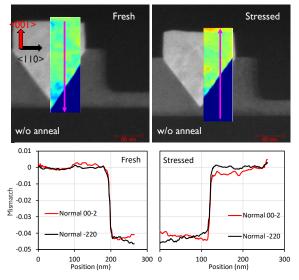

This assumption is further confirmed by using the strain TEM nano-beam diffraction technique (NBD) on a 'fresh' and electrically stressed device (150 °C and -5 V for 5000 h), without the seed annealing step. From Fig. 4, it can be depicted that there's no observable difference between the two samples. Some local strain is revealed, particularly in proximity of the defects, but the measured mismatch w.r.t. the reference (taken at the top GaAs) is very low and close to the sensitivity limit of the NDB method, for both.

Fig. 4: Comparison between an untreated and electrically stressed optical phase shifter, using strain TEM NBD technique, having similar trends without any difference manifesting in the strain.

## Electro-optical performance after stress

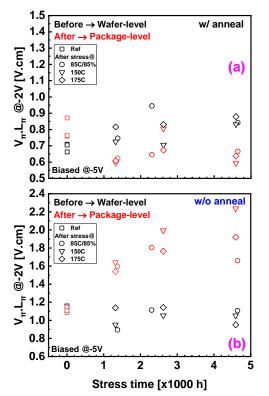

At different time intervals, the performance of stressed optical phase shifters was evaluated. Specifically, the monitored parameter is one that indicates the modulation efficiency,  $V_{\pi}.L_{\pi}$  which is the product of the voltage and the phase-shifter length for a  $\pi$ -phase shift. All measurements were performed at room temperature and the extracted values are compared with the wafer-level *t*<sub>0</sub> data in Fig. 5.

Data points at zero stress time, represent the reference, un-stressed devices in each case, that have been measured on wafer-level (in black) and on package-level (in red). For the phase shifters subjected to the additional seed annealing step,  $V_{\pi}.L_{\pi}$  values appear to be already very low before stress, while they remain unaffected for up to 5000 h of electrical stress. On the other hand, the components without this extra process step, are gradually degrading w.r.t. the applied stress time. The fact that different temperatures lead to similar degradation trends indicates that the observed degradation is a more bias-driven effect than a temperature related one.

Fig. 5:  $V_{\pi}.L_{\pi}$  values shift .w.r.t.  $t_{\text{stress}}$  for different stress conditions. Devices with (a) seed anneal appear to have an improved performance, while the ones without (b) are gradually degrading.

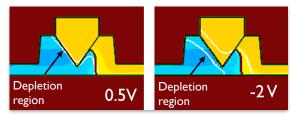

It is known that the  $V_{\pi}.L_{\pi}$  is inversely proportional to the change of the effective refractive index ( $\Delta n_{\text{eff}}$ ) that is directly correlated to the depletion width of the junction and therefore, with the junction capacitance. From Fig. 6, we can see that the higher reverse bias is applied, the wider the depletion region becomes, covering completely the GaAs/Si interface.

Fig. 6: Depletion width of the vertical p-n junction becoming wider with increasing reverse bias, pointing out to the contribution of the interface quality to the junction capacitance.

One possible explanation for the optical stability of the annealed devices, is the passivation, due to high temperature, of the preexisting dangling bonds. On the other hand, the phase shifters, not being subjected to the seed annealing step, are potentially experiencing an increase of the dangling bonds with longer stress times, that eventually leads to the measured  $V_{\pi}.L_{\pi}$  increase.

### Conclusions

Mo3F.6

A detailed reliability study on GaAs/Si p-n diode optical phase shifters was presented in this work. The long-term stability of the modulators was evaluated w.r.t. an optional seed annealing process step between the two-step epitaxy process. Dark current remains stable after up to 5000 h of electrical stress, at different conditions. Finally, the seed annealing step at 530 °C, can be used to revoke the modulation efficiency  $(V_{\pi}.L_{\pi})$  degradation before and after stress.

#### Acknowledgements

This work was supported by imec's industrial affiliation R&D program on Optical I/O. In particular, the members of the MCA group are acknowledged for FIB specimen preparation and TEM analysis.

## References

- G. Sinatkas, T. Christopoulos, O. Tsilipakos, and E. E. Kriezis, "Electro-optic modulation in integrated photonics," *Journal of Applied Physics*, vol. 130, no. 1, p. 010901, Jul. 2021, DOI: <u>10.1063/5.0048712</u>.

- [2] Y. Kim, J.-H. Han, D. Ahn, and S. Kim, "Heterogeneously-Integrated Optical Phase Shifters for Next-Generation Modulators and Switches on a Silicon Photonics Platform: A Review," *Micromachines*, vol. 12, no. 6, p. 625, May 2021, DOI: <u>10.3390/mi12060625</u>.

- [3] C. I. Ozdemir, Y. de Koninck, D. Yudistira, N. Kuznetsova, M. Baryshnikova, D. van Thourhout, B. Kunert, M. Pantouvaki, and J. van Campenhout, "0.3pA Dark Current and 0.65A/W Responsivity 1020nm InGaAs/GaAs Nano-Ridge Waveguide Photodetector Monolithically Integrated on a 300-mm

Si Wafer," in 2020 European Conference on Optical Communications (ECOC), Brussels, Belgium, Dec. 2020, pp. 1–4. DOI: 10.1109/ECOC48923.2020.9333310.

- [4] P. Absil et al., "Reliable 50Gb/s silicon photonics platform for next-generation data center optical interconnects," Dec. 2017, p. 34.2.1-34.2.4. DOI: 10.1109/IEDM.2017.8268494.

- [5] M. Pantouvaki, S. A. Srinivasan, Y. Ban, P. De Heyn, P. Verheyen, G. Lepage, H. Chen, J. De Coster, N. Golshani, S. Balakrishnan, P. Absil, and J. Van Campenhout, "Active Components for 50 Gb/s NRZ-OOK Optical Interconnects in a Silicon Photonics Platform," *Journal of Lightwave Technology*, vol. 35, no. 4, pp. 631–638, Feb. 2017, DOI: 10.1109/JLT.2016.2604839.

- [6] K. Yamada, T. Tsuchizawa, H. NISHI, R. Kou, T. Hiraki, K. Takeda, and H. Fukuda, "Silicon-Germanium-Silica Monolithic Photonic Integration Platform for High-Performance Optical Data Communication Systems," in ECS Transactions, Oct. 2014, vol. 64. DOI: <u>10.1149/06406.0749ecst</u>.

- [7] C. Shang, J. Selvidge, E. Hughes, J. C. Norman, A. A. Taylor, A. C. Gossard, K. Mukherjee, and J. E. Bowers, "A Pathway to Thin GaAs Virtual Substrate on On-Axis Si (001) with Ultralow Threading Dislocation Density," *physica status solidi* (a), vol. 218, no. 3, p. 2000402, 2021, DOI: <u>https://doi.org/10.1002/pssa.202000402</u>.

- [8] Y. Kim, S. Kim, Y. Ban, S. Lardenois, D. Yudistira, M. Pantouvaki, and J. Van Campenhout, "Proposal and Simulation of a Low Loss, Highly Efficient Monolithic III-V/Si Optical Phase Shifter," in 2019 IEEE 16th International Conference on Group IV Photonics (GFP), 2019, pp. 1–2. DOI: 10.1109/GROUP4.2019.8926128.

- [9] S. Kim, Y. Kim, Y. Ban, M. Pantouvaki, and J. Van Campenhout, "Simulation Study of a Monolithic III-V/Si V-Groove Carrier Depletion Optical Phase Shifter," *IEEE Journal of Quantum Electronics*, vol. 56, no. 2, pp. 1–8, Apr. 2020, DOI: <u>10.1109/JQE.2020.2971764</u>.

- [10] Y. Kim, D. Yudistira, B. Kunert, M. Baryshnikova, R. Alcotte, C. Ozdemir, S. Kim, S. Lardenois, P. Verheyen, J. Van Campenhout, and M. Pantouvaki, "Monolithic GaAs/Si V-groove depletion-type optical phase shifters integrated in a 300mm Si photonics platform," *Photonics Research*, Mar. 2022, DOI: 10.1364/PRJ.451821.

- [11] T. Nishioka, Y. Itoh, M. Sugo, A. Yamamoto, and M. Yamaguchi, "Threading Dislocation Density Reduction in GaAs on Si Substrates," *Japanese Journal of Applied Physics*, vol. 27, no. Part 2, No. 12, pp. L2271– L2273, Dec. 1988, DOI: <u>10.1143/JJAP.27.L2271</u>.

- [12] M. Yamaguchi, M. Tachikawa, Y. Itoh, M. Sugo, and S. Kondo, "Thermal annealing effects of defect reduction in GaAs on Si substrates," *Journal of Applied Physics*, vol. 68, no. 9, pp. 4518–4522, Nov. 1990, DOI: <u>10.1063/1.346156</u>.

- [13] H. Shimomura, Y. Okada, H. Matsumoto, M. Kawabe, Y. Kitami, and Y. Bando, "Reduction Mechanism of Dislocation Density in GaAs Films on Si Substrates," *Japanese Journal of Applied Physics*, vol. 32, no. Part 1, No. 1B, pp. 632–636, Jan. 1993, DOI: <u>10.1143/JJAP.32.632</u>.

- [14] Y. Takagi, H. Yonezu, Y. Hachiya, and K. Pak, "Reduction Mechanism of Threading Dislocation Density in GaAs Epilayer Grown on Si Substrate by High-Temperature Annealing," *Japanese Journal of*

Applied Physics, vol. 33, no. Part 1, No. 6A, pp. 3368–3372, Jun. 1994, DOI: <u>10.1143/JJAP.33.3368</u>.

- [15] M. Tamura, T. Yodo, T. Saitoh, and J. Palmer, "Rearrangement of misfit dislocations in GaAs on Si by post-growth annealing," *Journal of Crystal Growth*, vol. 150, pp. 654–660, 1995, DOI: <u>https://doi.org/10.1016/0022-0248(95)80290-S</u>.

- [16] H. Y. Xu, Y. N. Guo, Y. Wang, J. Zou, J. H. Kang, Q. Gao, H. H. Tan, and C. Jagadish, "Effects of annealing and substrate orientation on epitaxial growth of GaAs on Si," *Journal of Applied Physics*, vol. 106, no. 8, p. 083514, Oct. 2009, DOI: <u>10.1063/1.3248372</u>.

- [17] B. Kunert, Y. Mols, M. Baryshniskova, N. Waldron, A. Schulze, and R. Langer, "How to control defect formation in monolithic III/V hetero-epitaxy on (100) Si? A critical review on current approaches," *Semiconductor Science and Technology*, vol. 33, no. 9, p. 093002, Sep. 2018, DOI: <u>10.1088/1361-6641/aad655</u>.

- [18] W. Guo, Y. Mols, J. Belz, A. Beyer, K. Volz, A. Schulze, R. Langer, and B. Kunert, "Anisotropic relaxation behavior of InGaAs/GaAs selectively grown in narrow trenches on (001) Si substrates," *Journal of Applied Physics*, vol. 122, no. 2, p. 025303, 2017, DOI: 10.1063/1.4991481.