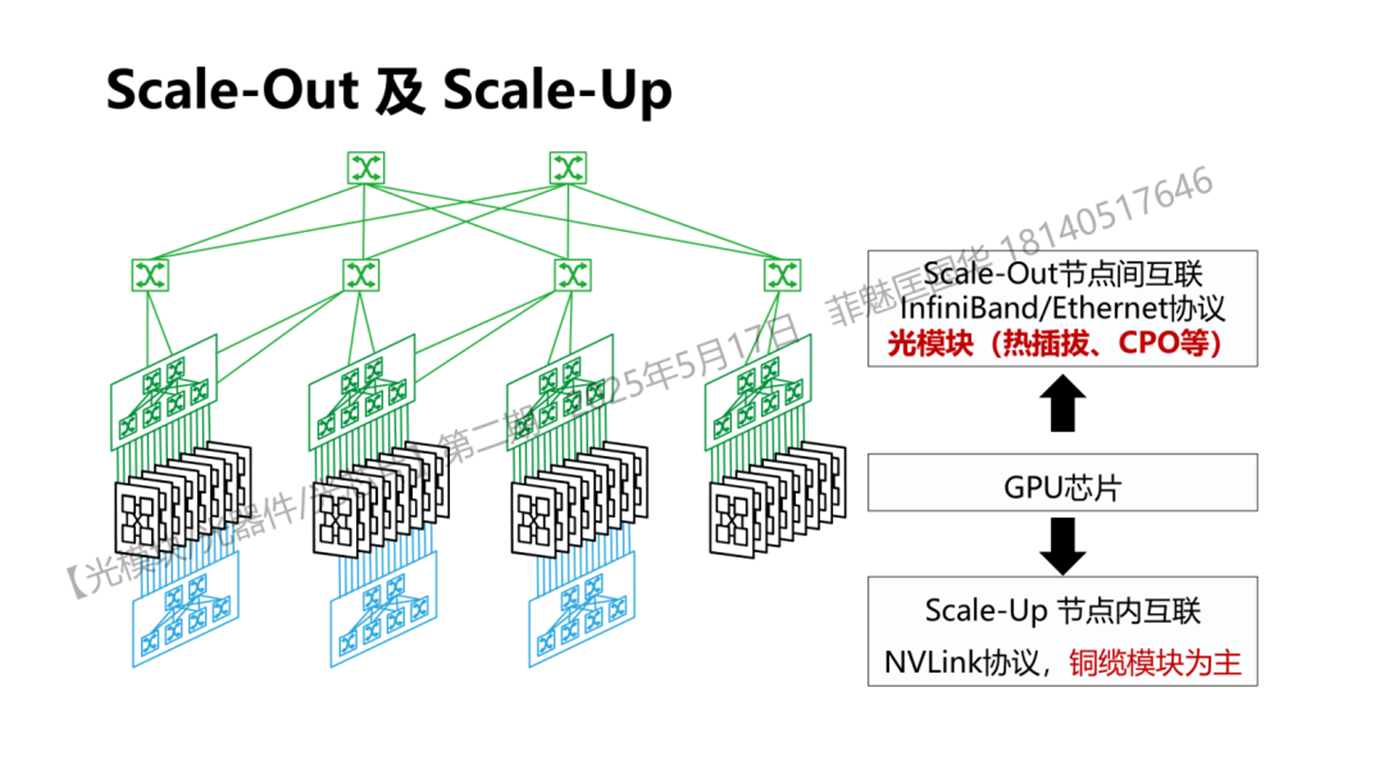

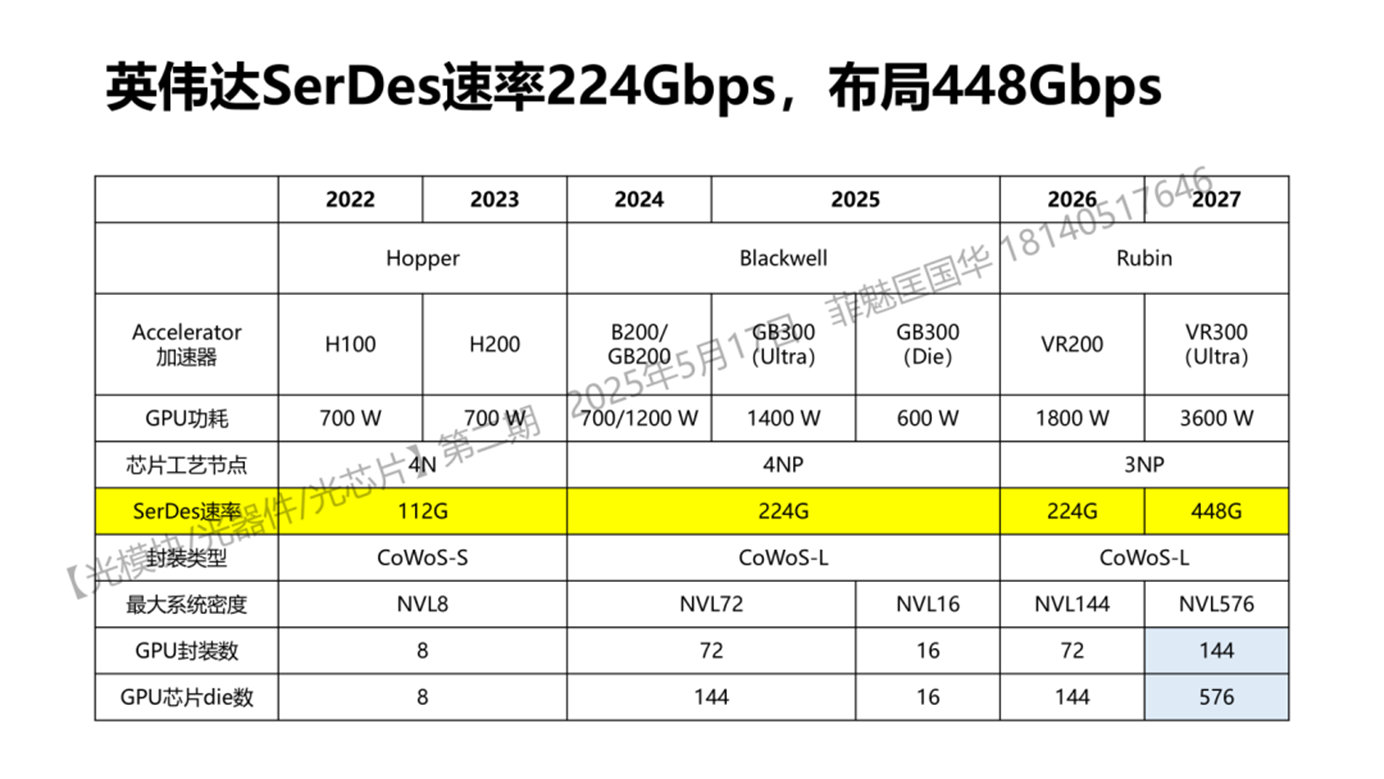

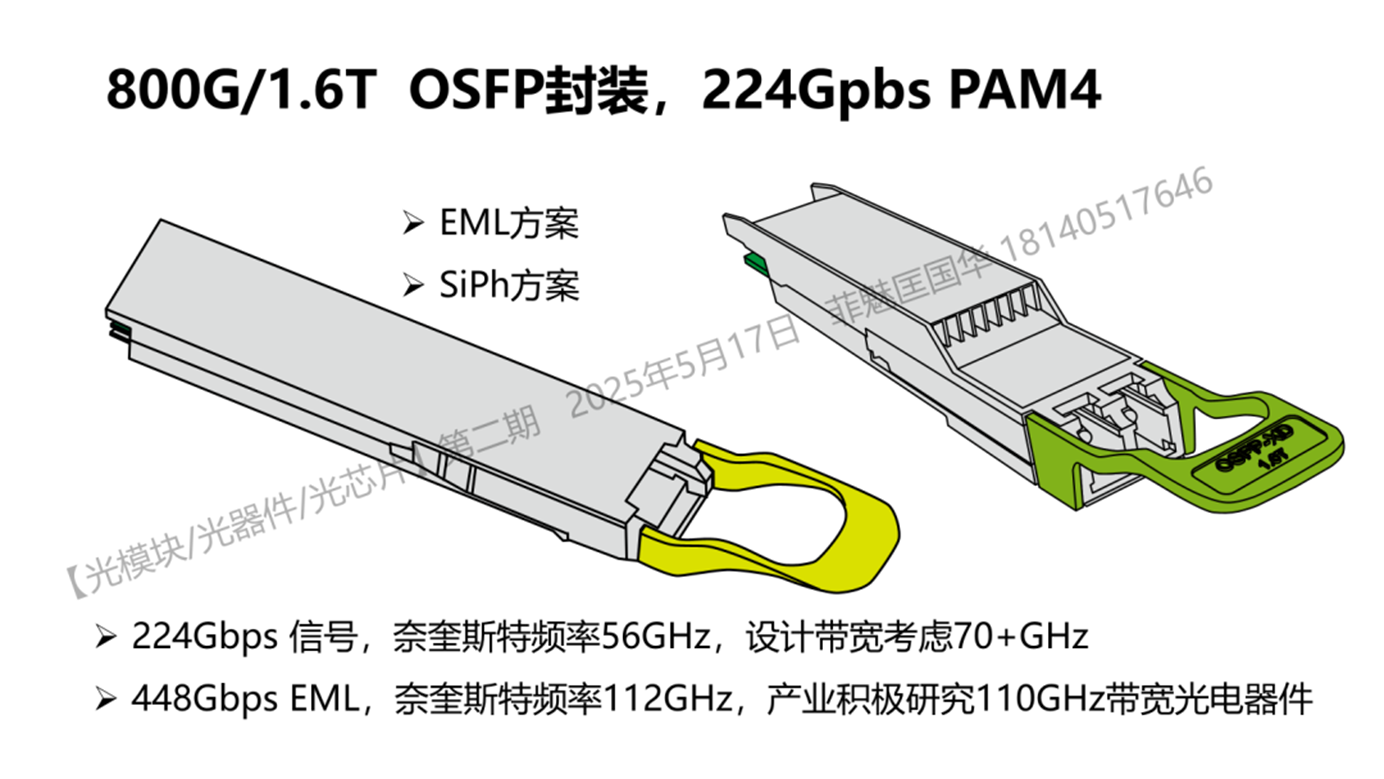

人工智能AI需要非常大的算力,Scale up的铜缆模块,今年我做了一个解析,Scale-out则以光模块为主,一方面是热插拔的传统光模块向单lane 224Gbps PAM4的800G、1.6T发展,另一方面CPO提上了日程。

无论是电缆模块,还是传统的热插拔光模块,甚至是CPO,当前都需要考虑112Gbps PAM4的信号处理如何向224Gbps PAM4的更高速信号的优化。

一些大厂,以及积极研究448Gbps PAM4的各种光电芯片技术以及封装技术了。

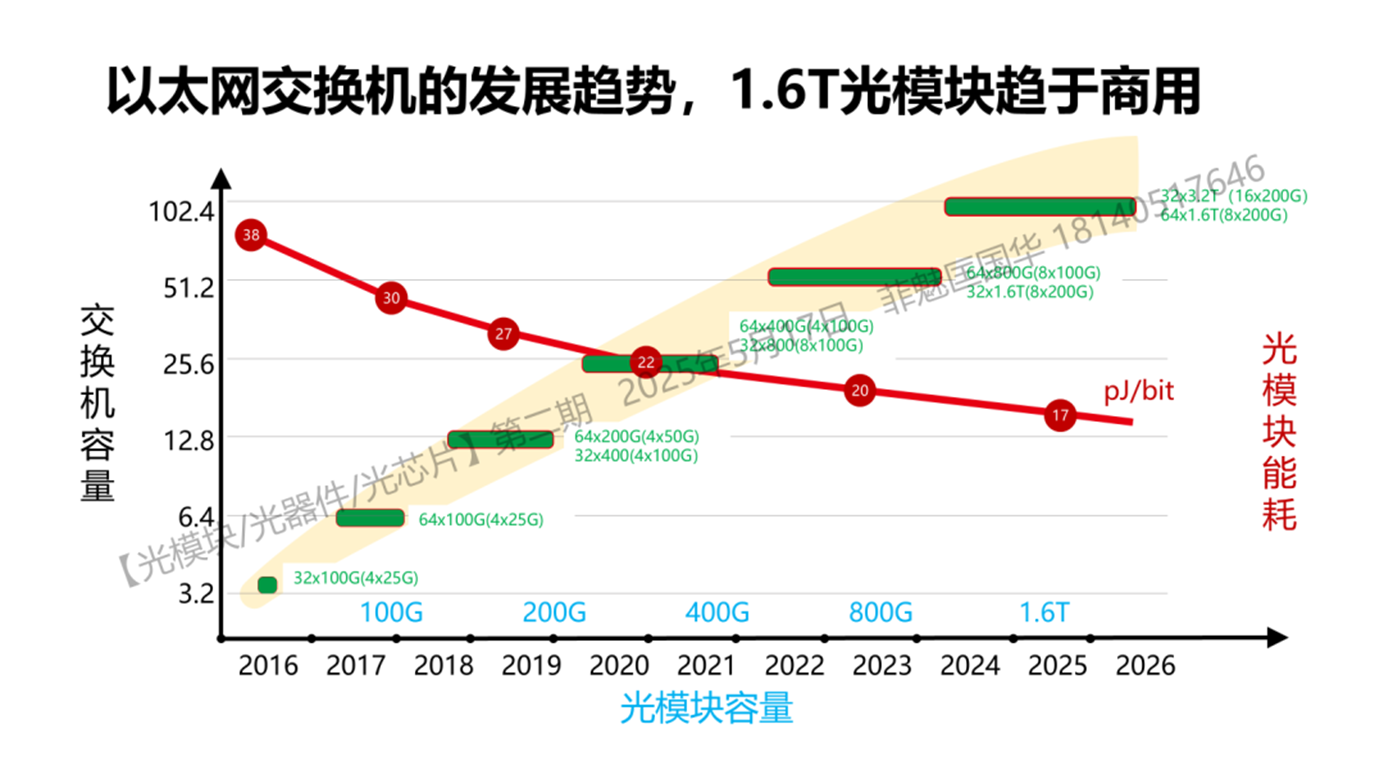

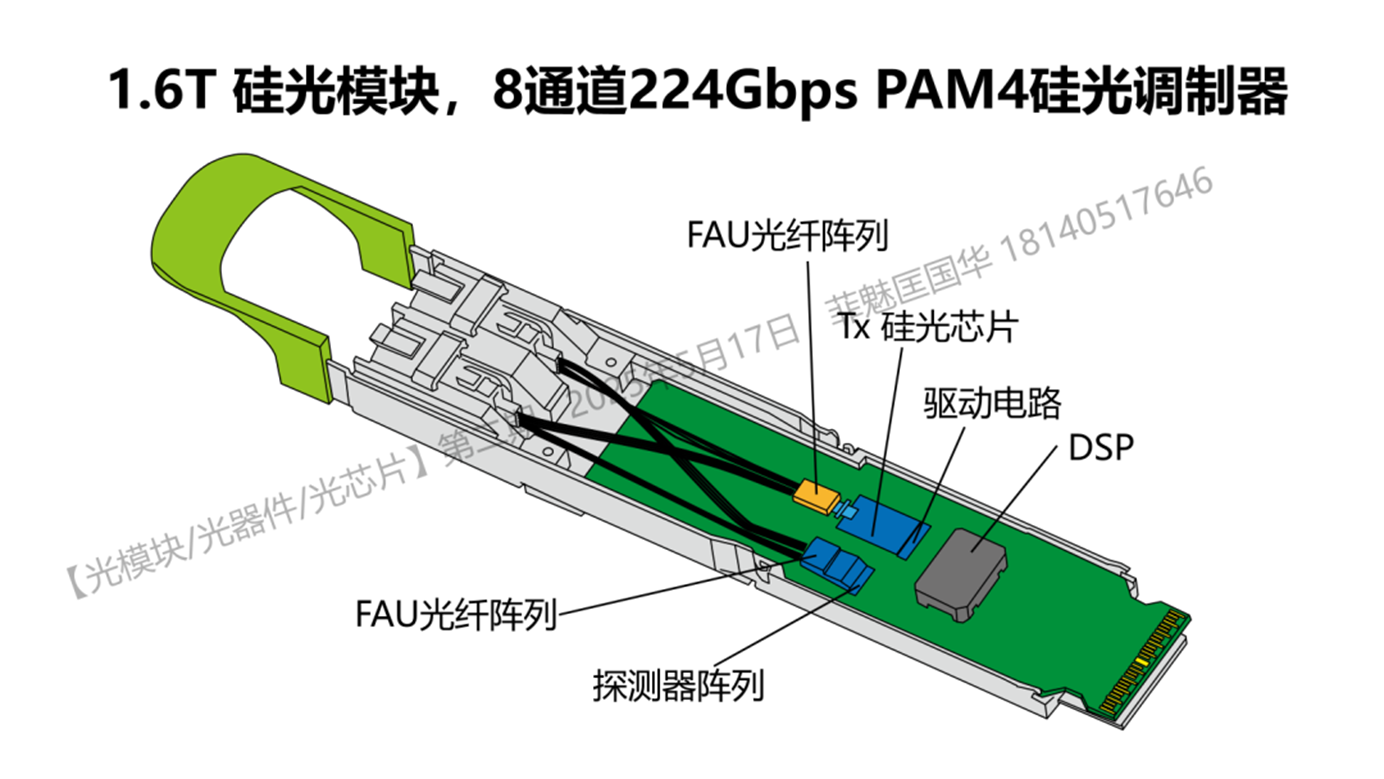

2025年,1.6T光模块会有商用的苗头,意味着技术从实验室的研究状态转向产业应用。

备注一下哈,200Gbps PAM4 的纯业务信号,考虑了编码后会实际变成212Gbps PAM4或者是224Gbps PAM4。

200Gbps PAM4、212Gbps PAM4、224Gbps PAM4在特定场景的描述里看似不同,实则相同。

就像很多小姑娘称体重,净重50kg,与穿衣服体重51kg,穿衣服鞋子体重52kg,都是对同一个姑娘的体重描述。重点是这个姑娘没变。

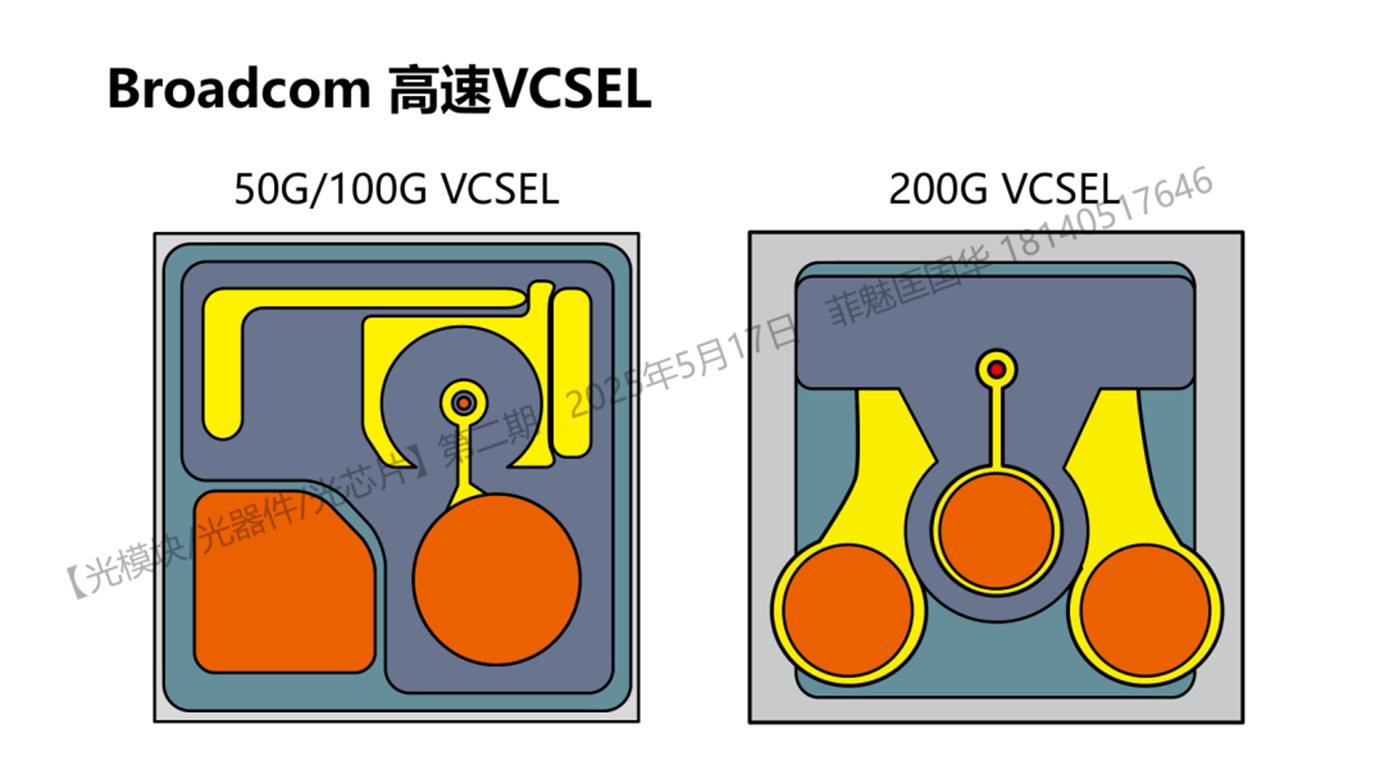

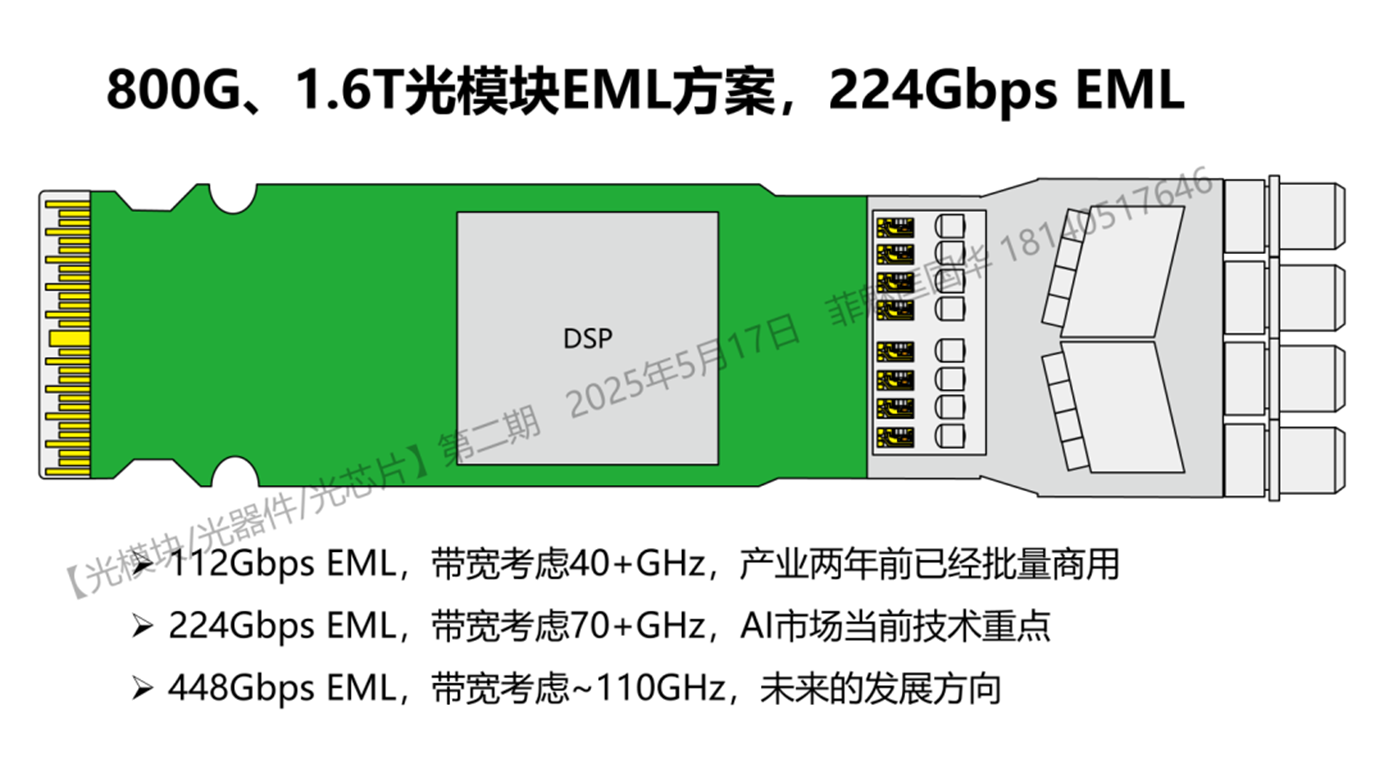

整个产业多模选择VCSEL,单模选择EML或者硅光,在信号频率带宽与比特率、波特率之间,有个换算关系。

VCSEL的带宽发展略低于EML和硅光。目前多模VCSEL产业是部署100Gbps PAM4,研究200Gbps PAM4,而EML和硅光则是部署200Gbps PAM4,研究400Gbps PAM4,技术限制导致的带宽发展差异。

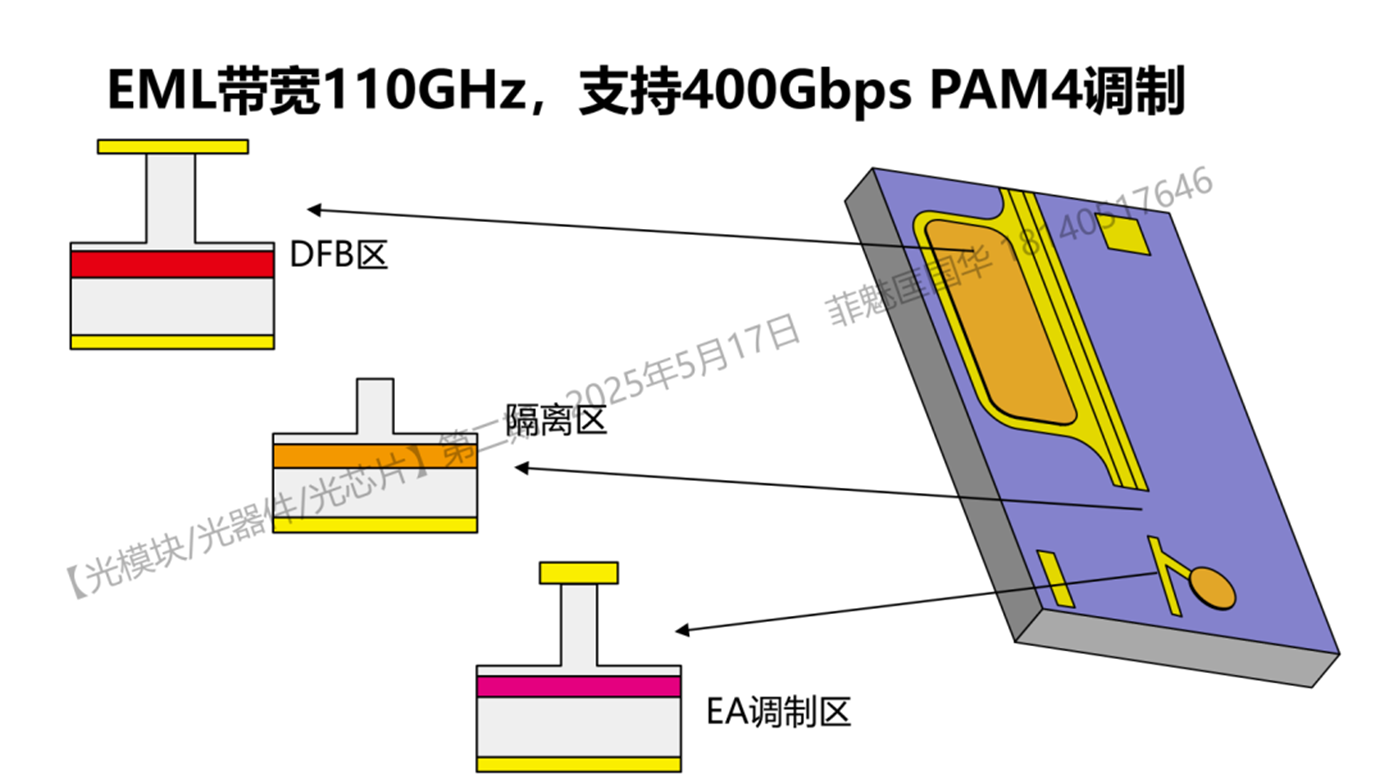

Lumentum、Broadcom、三菱....,华为海思等,都在积极研究224Gbps EML以及300+G、400+Gbps的更高速率芯片。

下图海思的EML带宽,今年进展到110GHz,目的是支持400Gbps PAM4以上的调制信号速率,采用更高阶的编码如PAM6/8,可以支持500Gbps以上的比特率。

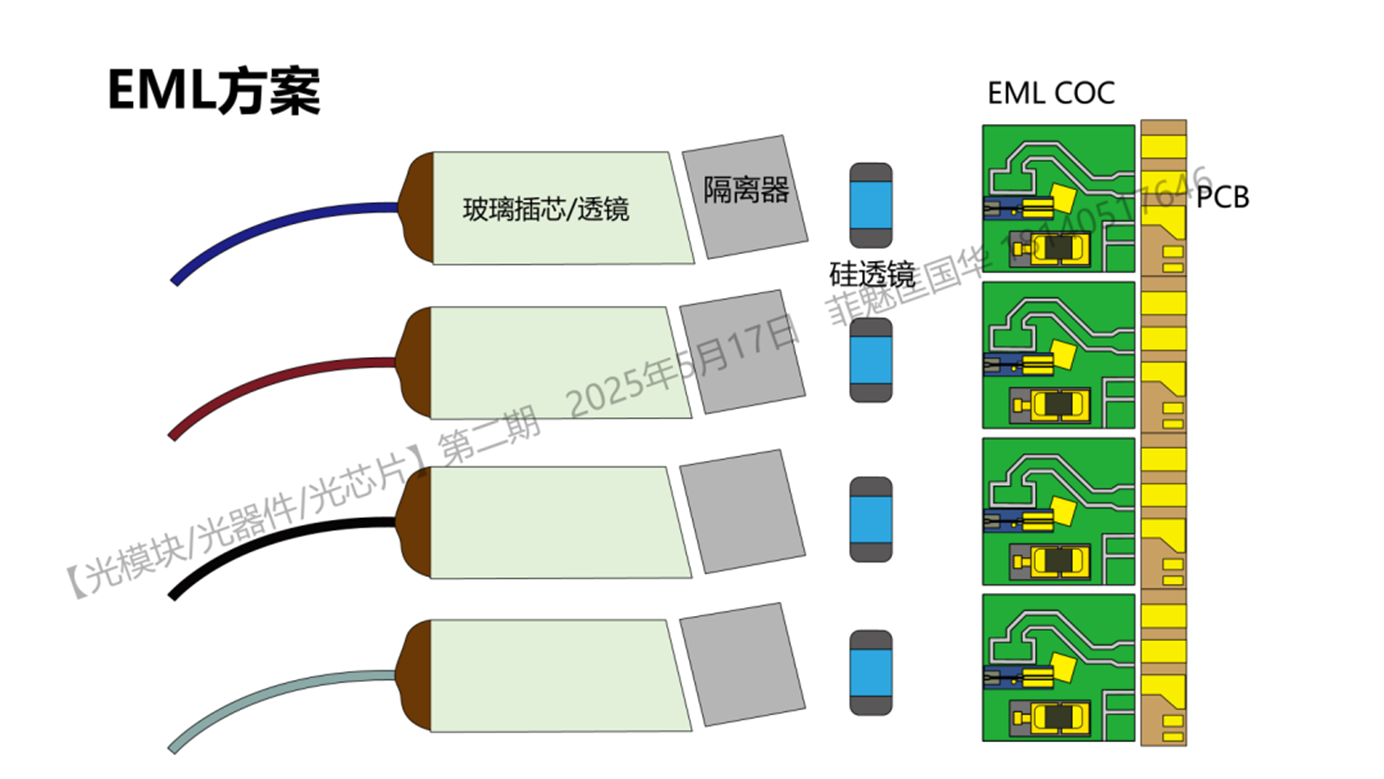

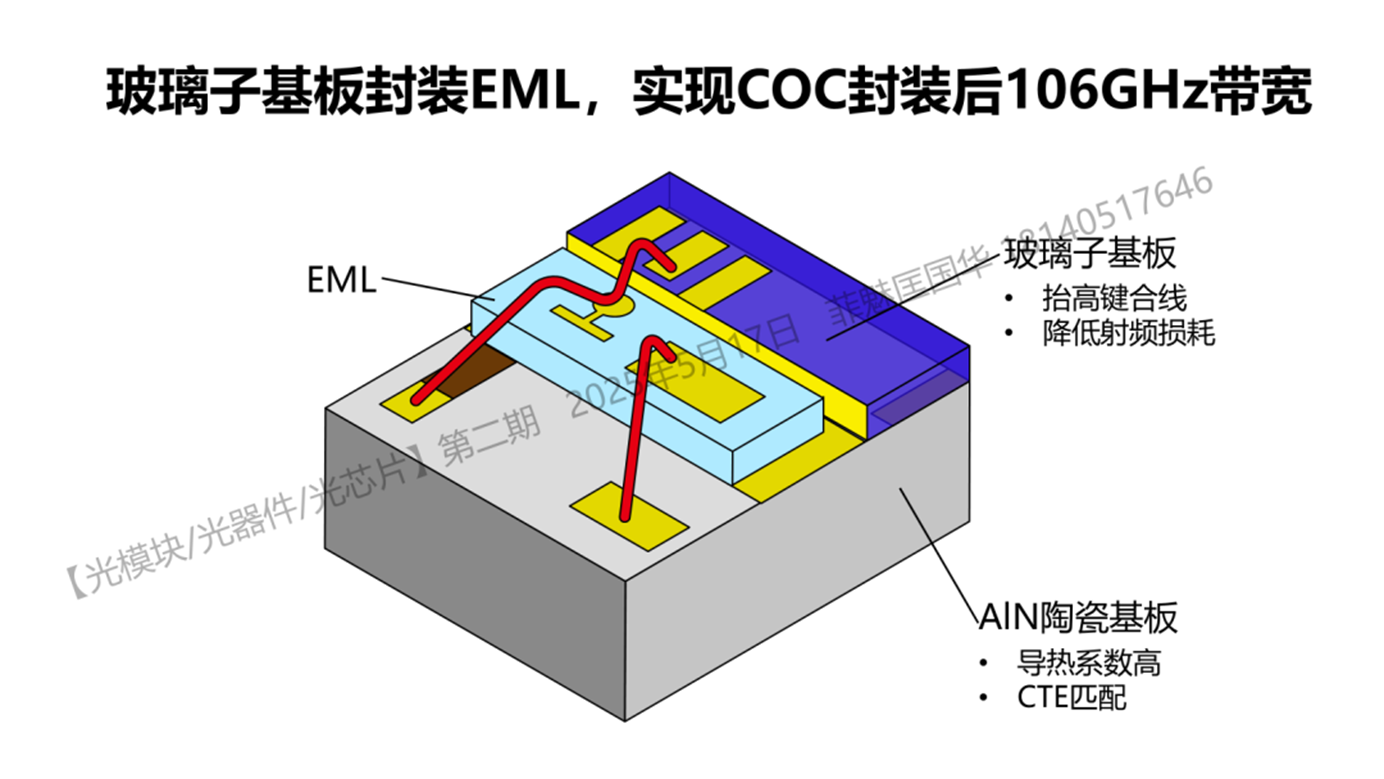

EML的封装,与整体工作带宽强相关,各种思路的试验与探讨。

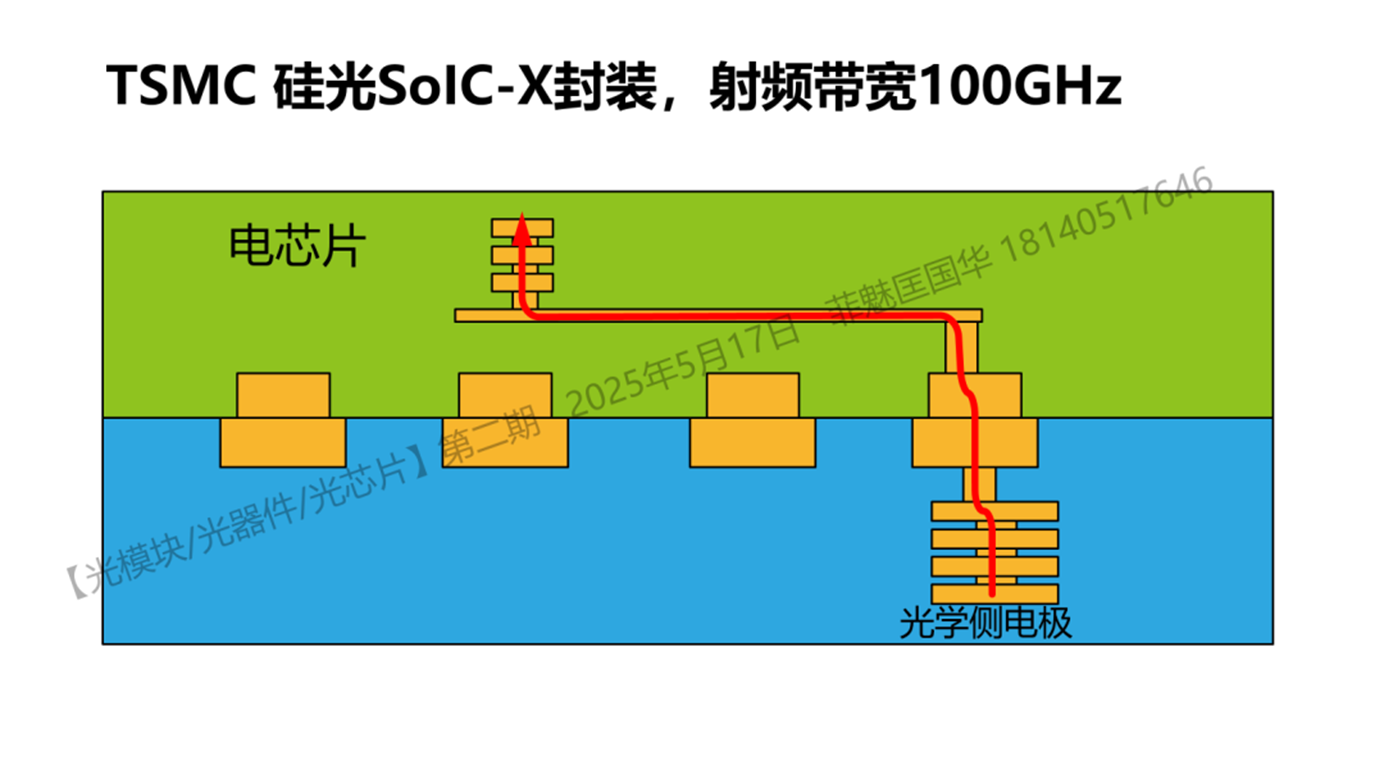

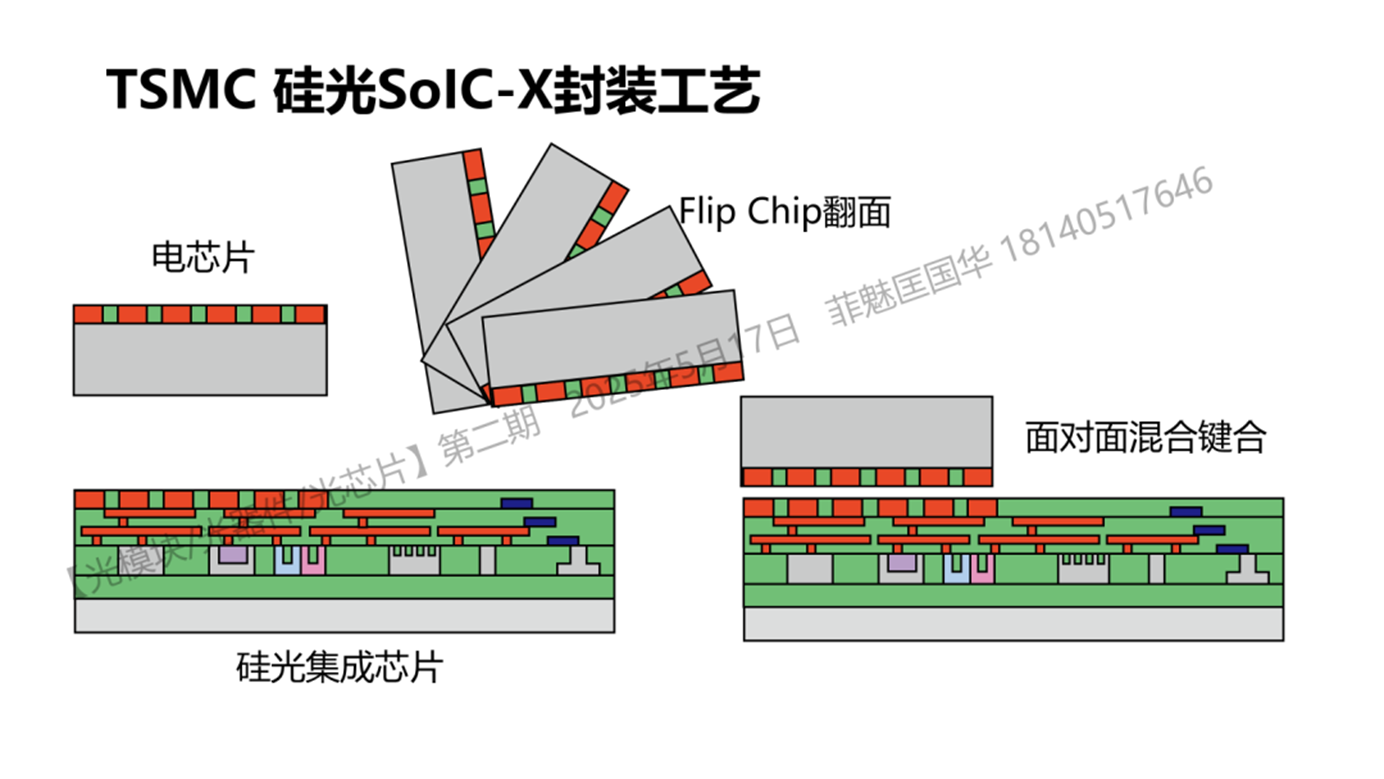

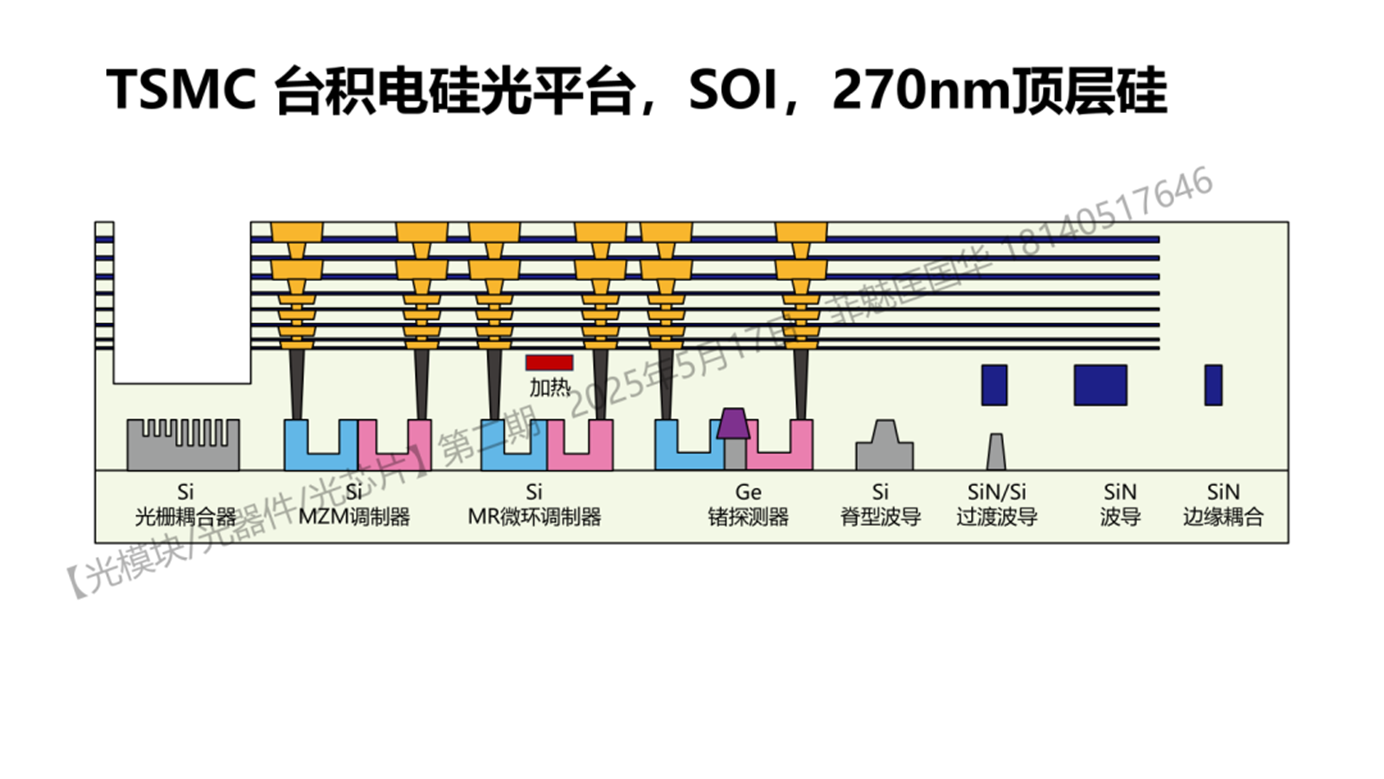

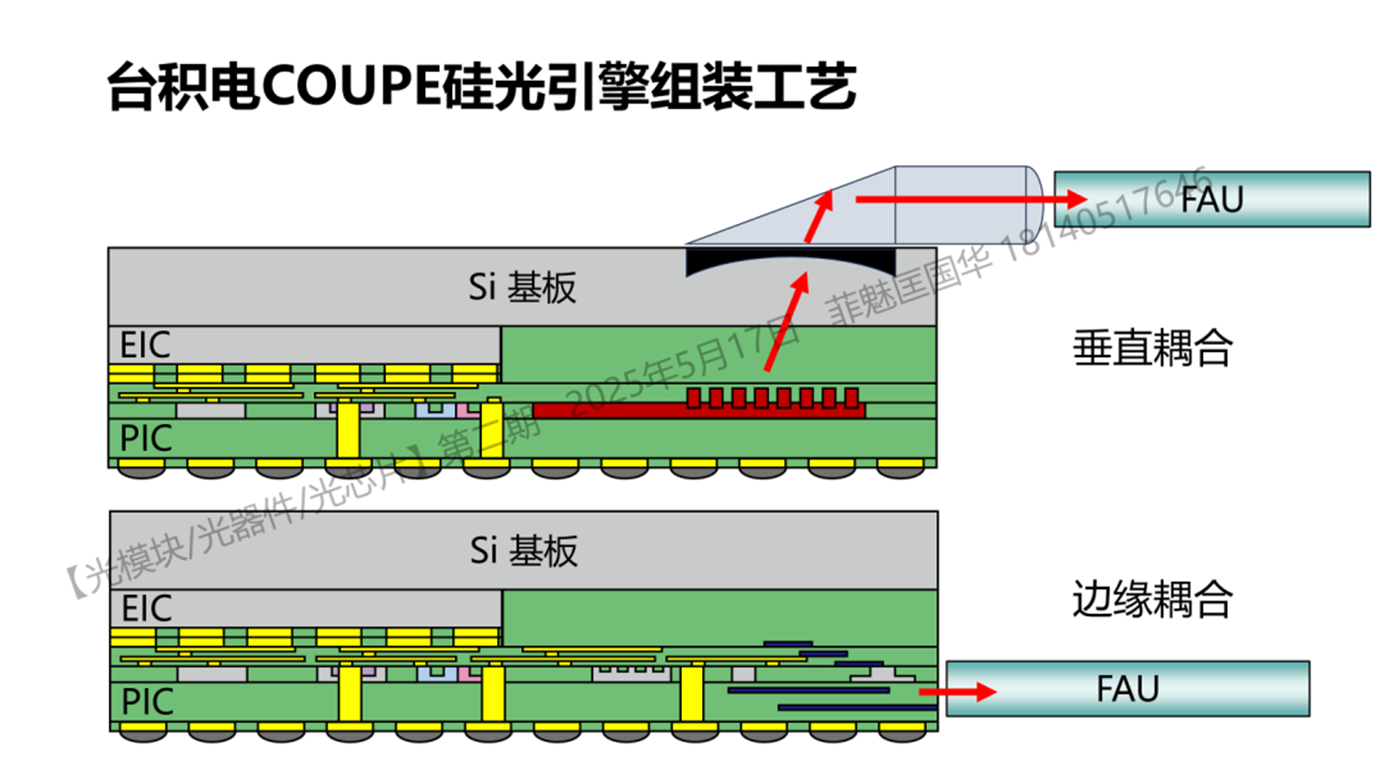

硅光成为一个产业的选择,除了集成度高的优势外,还有一个优势就是封装带宽很大,如台积电的硅光3D封装。

硅光模块在热插拔和CPO都有应用,也处于224Gbps PAM4的调制速率级别。但与EML的带宽相比,硅光还是有点勉强的。

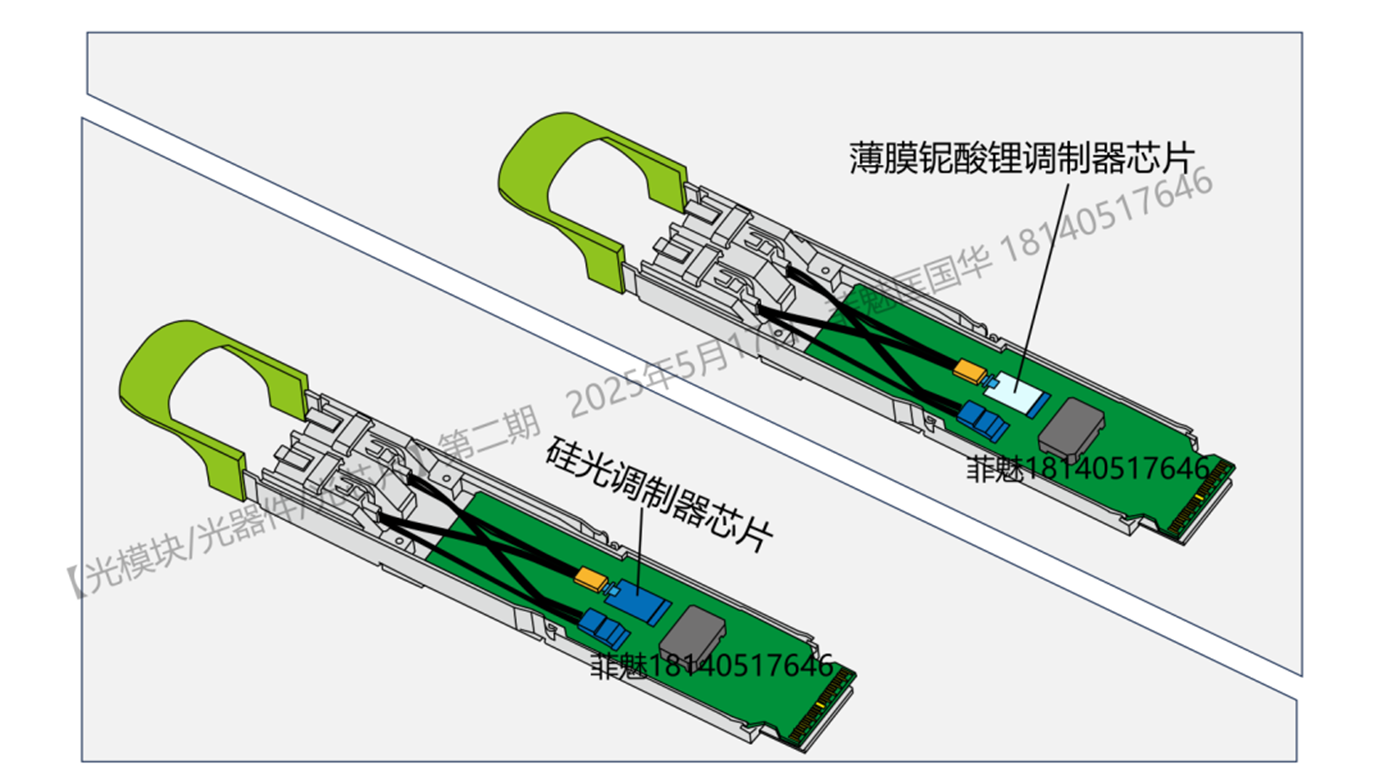

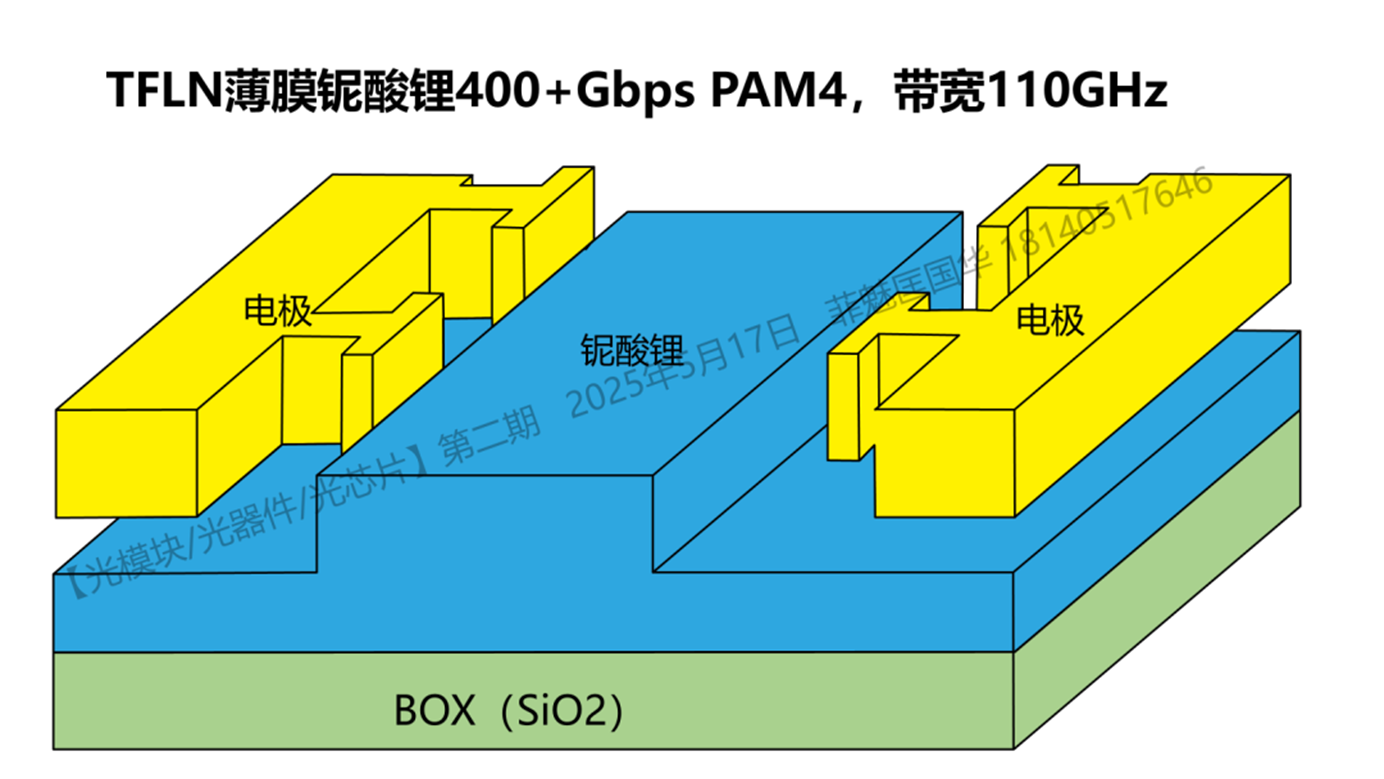

硅光的带宽相比EML略有勉强,薄膜铌酸锂具有更大的光学带宽,也成为一些研究者的技术探索之一,讨论能否在集成赛道里,既可以共用硅光的大带宽封装工艺平台,还可以实现调制器的大带宽提升。

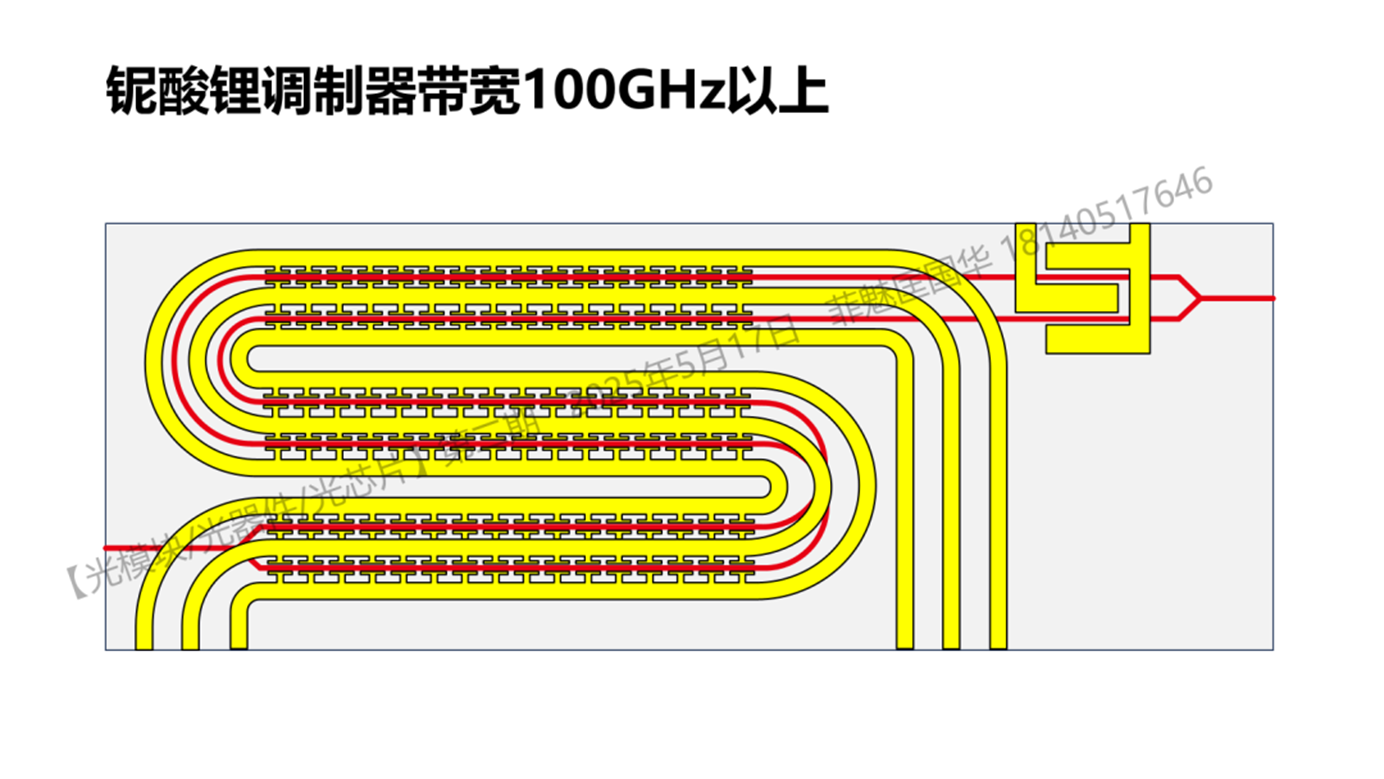

一些厂家通过各种设计,探讨100GHz及以上的铌酸锂调制器设计。

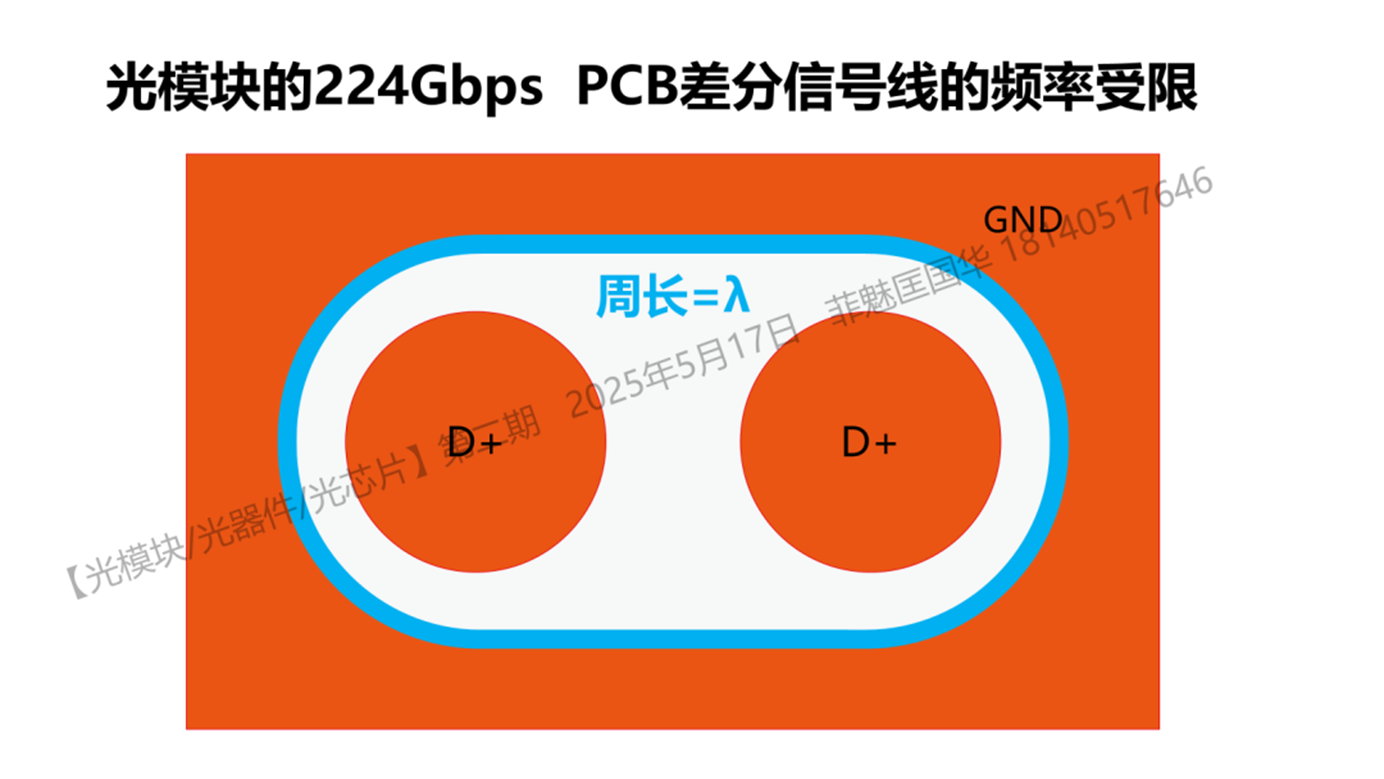

224Gbps PAM4的信号处理,光学芯片很难,PCB的电信号处理也不容易,过孔的寄生参数,差分信号的布局与回流,差分线的奇模偶模的控制,玻纤效应的影响,差分信号的skew时延....., 一系列的问题,都在影响PCB电信号的噪声、损耗以及自谐振。

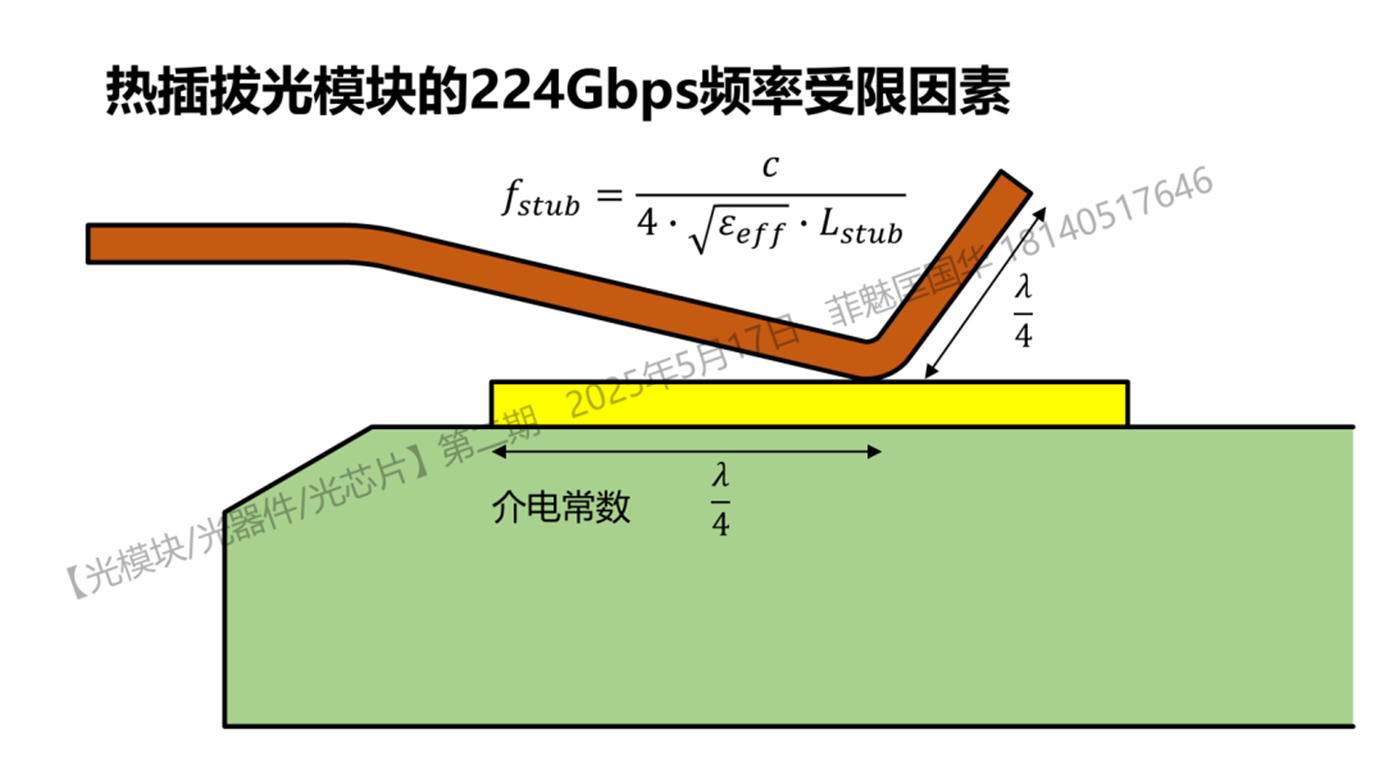

对于热插拔光模块而言,还有一个插座接触点与频率的限制。

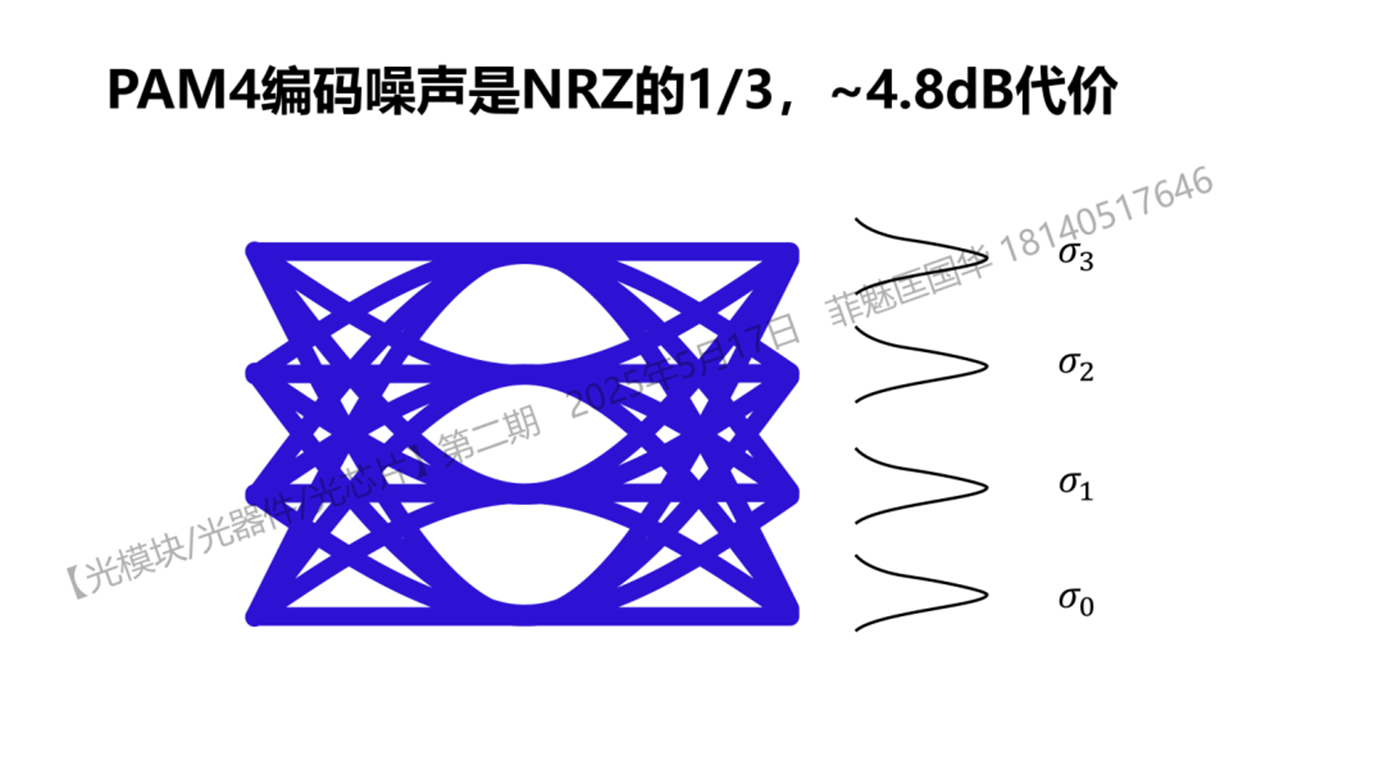

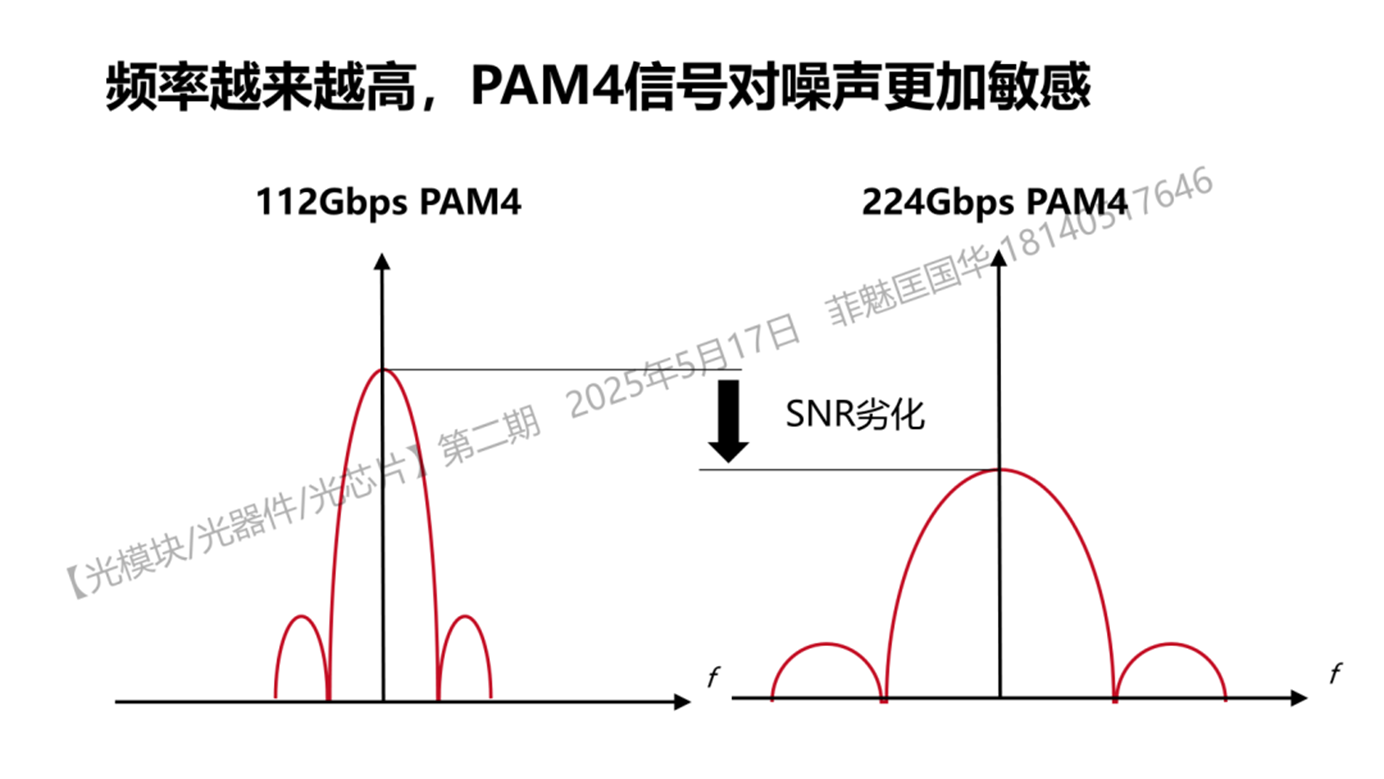

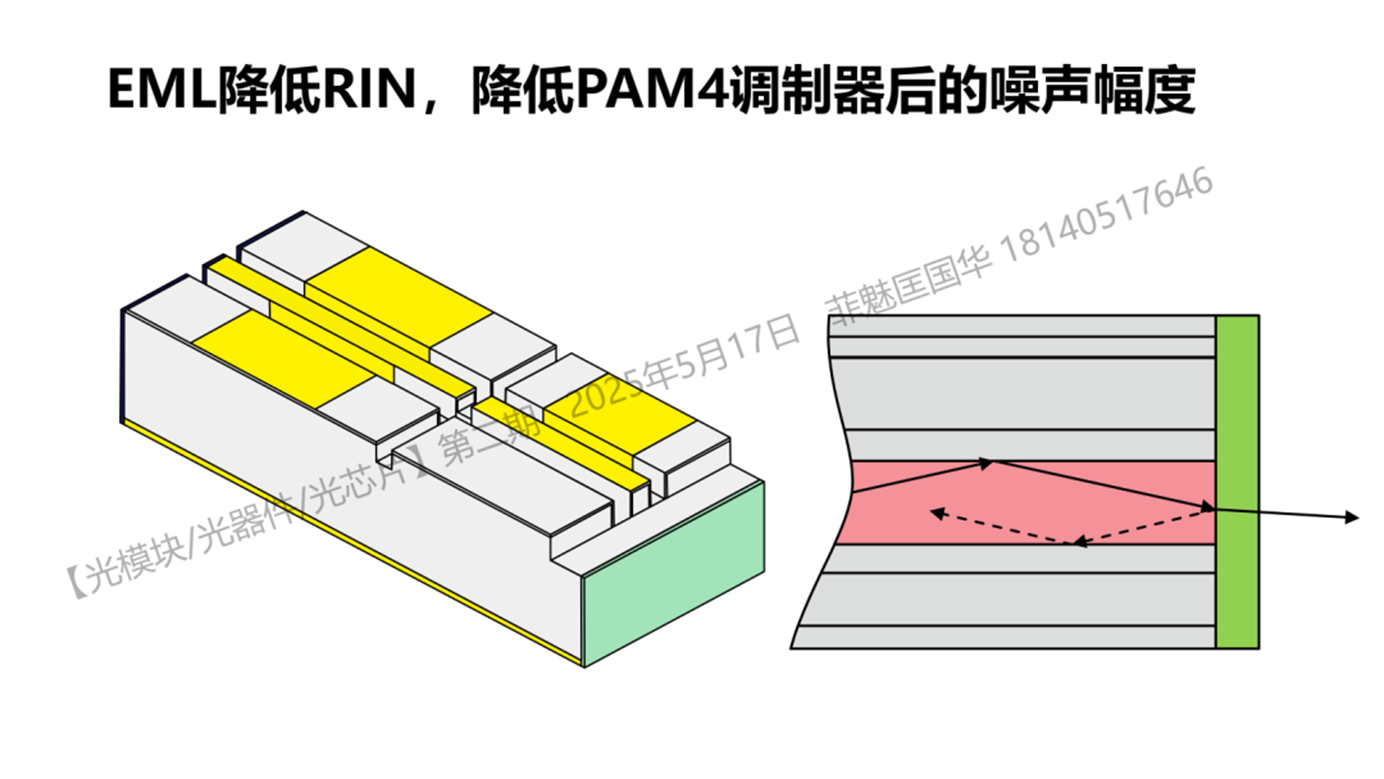

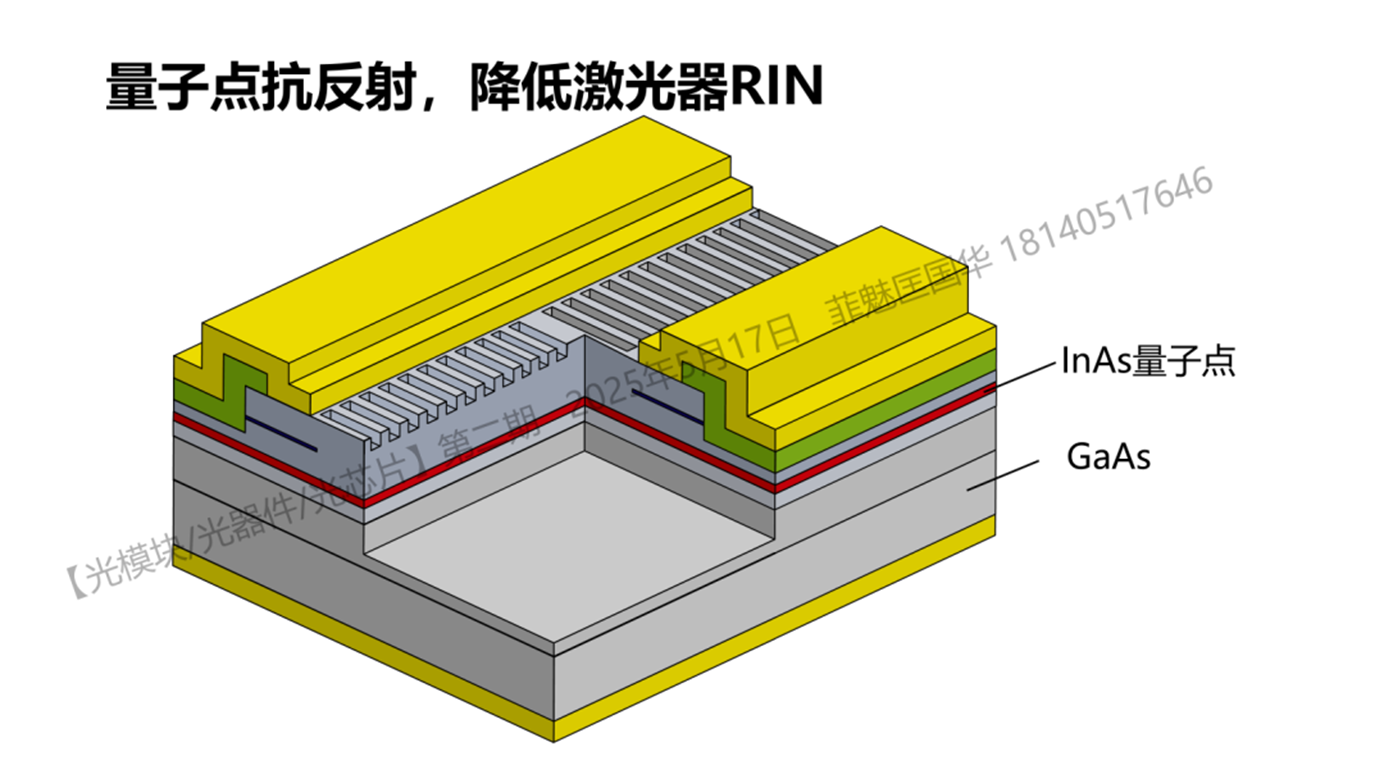

另外就是,800G、1.6T的高速光模块,信号处理十分艰难,PAM4本身对噪声就很敏感,SNR信噪比产生了4.8dB的编码导致的劣化。

频率提高,再次导致SNR的劣化。

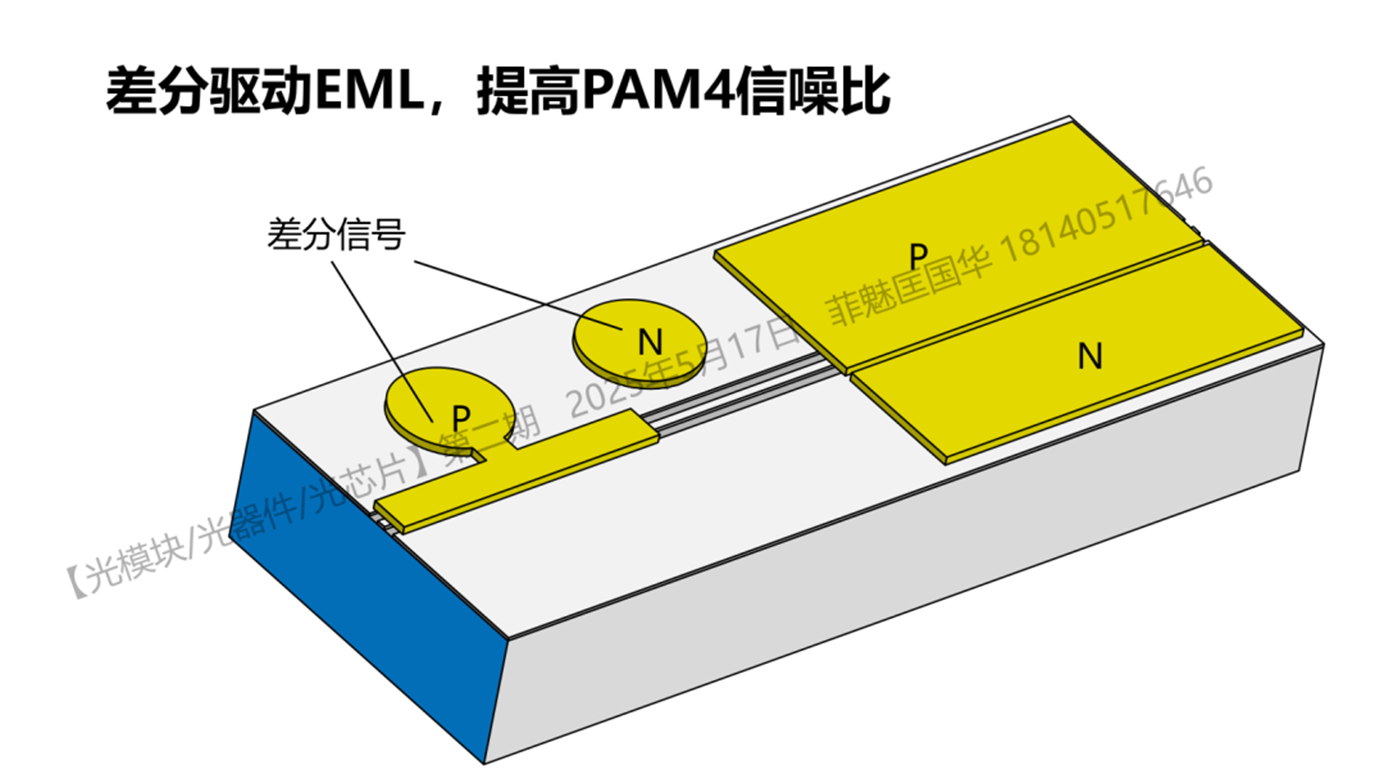

一方面,芯片来提高信号幅度,比如差分EML,提高SNR信噪比,SNR分子是信号,分母是噪声,提高信号幅度优化分子。

另一方面,想尽办法降低噪声,这是SNR信噪比的降低噪声这个分母。

PAM4对噪声敏感,高频信号对信噪比敏感,除了芯片本身优化信噪比外,DSP也会通过算法来优化或补偿信噪比。

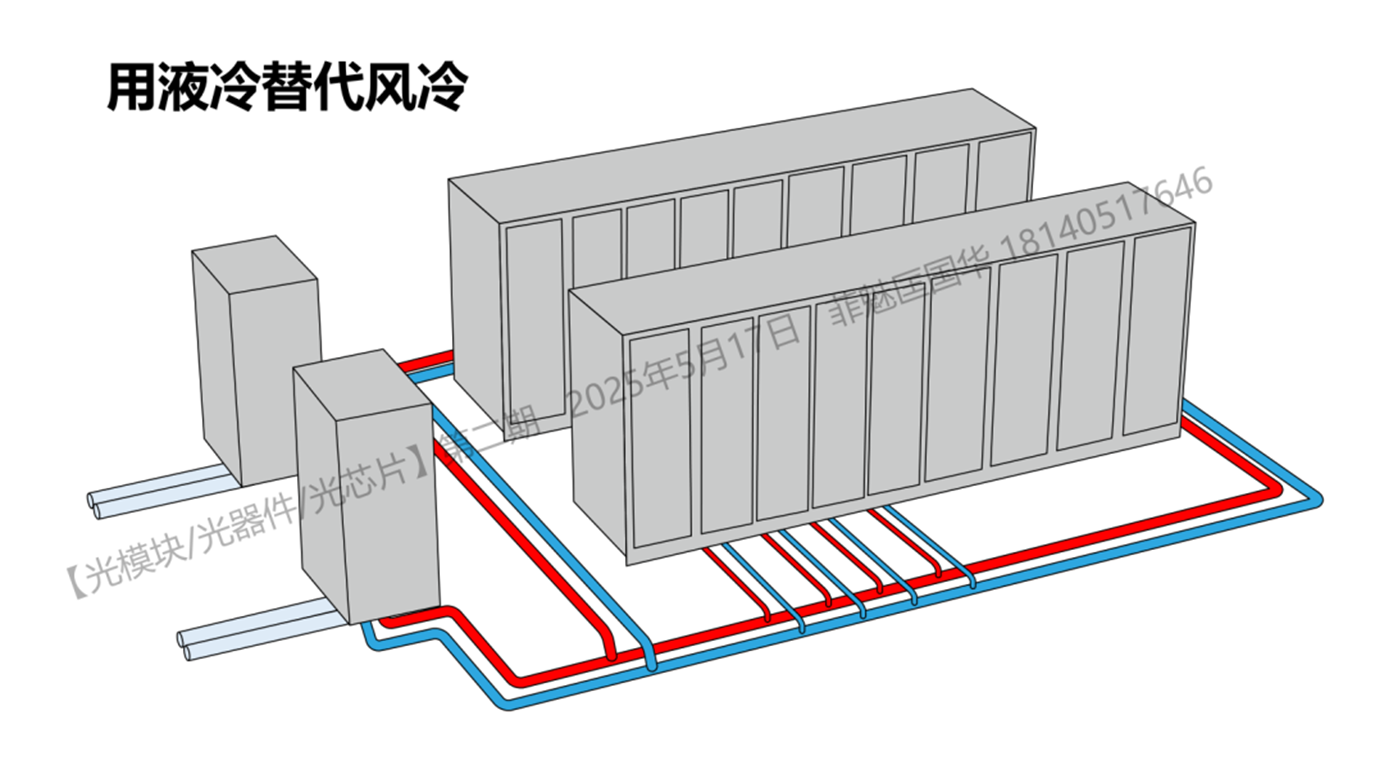

但DSP会带来巨大的功耗增加。光模块功耗很大,需要考虑散热,液冷在AI场景支持了更大的散热能力。

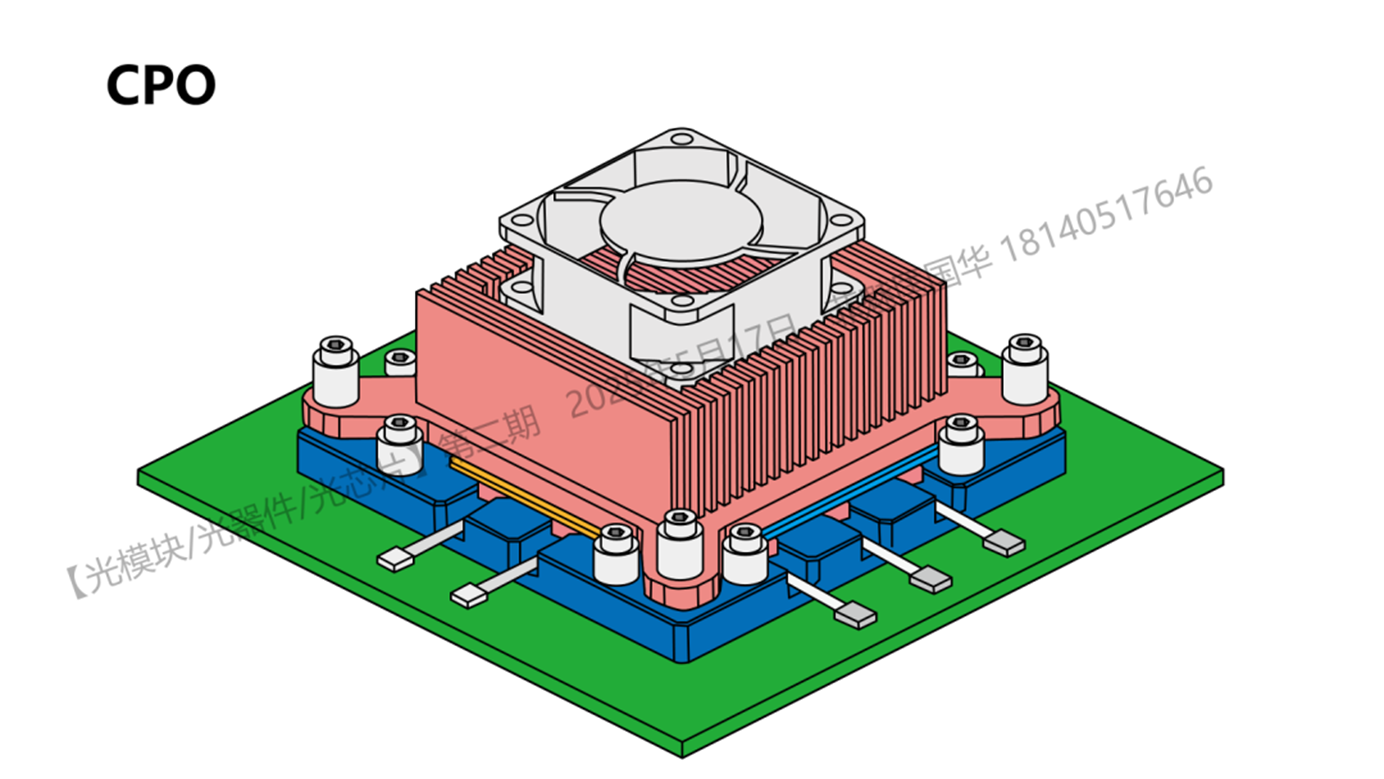

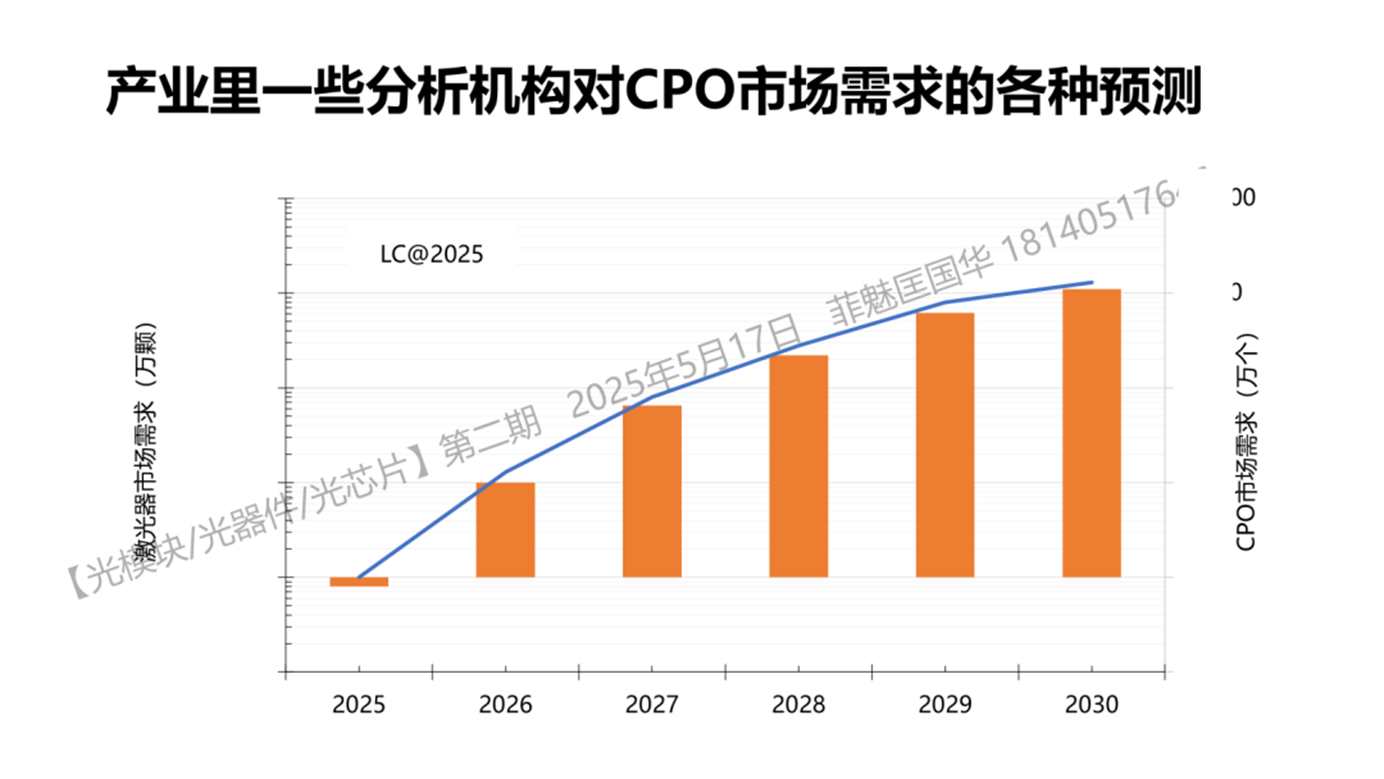

除了传统热插拔光模块外,LPO取消DSP,CPO的低功耗思路,也都提上日程,今年很关注的CPO,成为产业热点。

CPO有单模CPO,多模CPO,多模CPO采用VCSEL做光源,单模CPO考虑硅光方案。

硅光集成技术在在热插拔硅光模块,与CPO光引擎中,都有了很大的市场机会。

多个厂家推出自己的硅光平台,顶层硅160nm的、220nm的,270nm的,300nm的,400nm的等等。

氮化硅层,有单层的、多层的.....,也分了很多不同的细类。

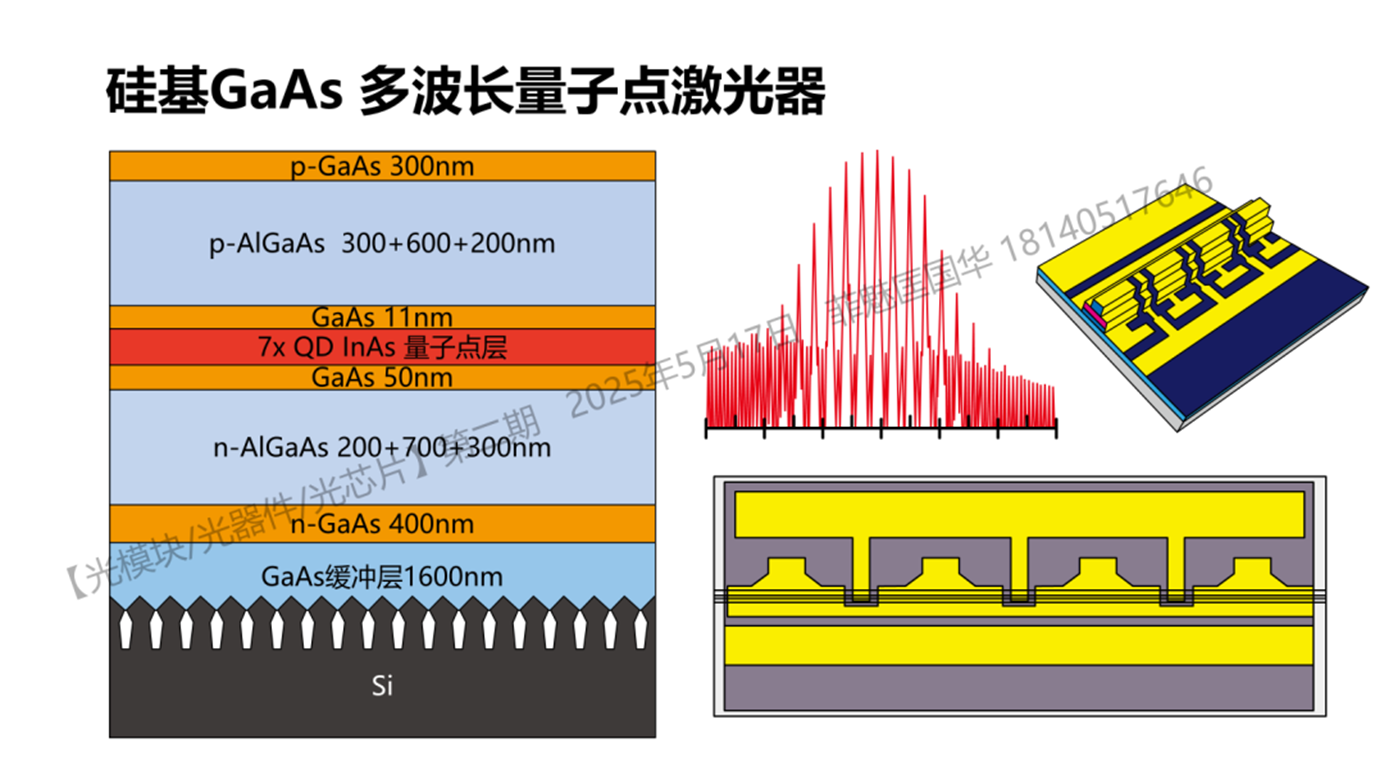

有硅上InP的,硅上GaAs的,硅上TFLN铌酸锂的,硅上BTO钛酸钡的,同样也是多样化的技术平台。

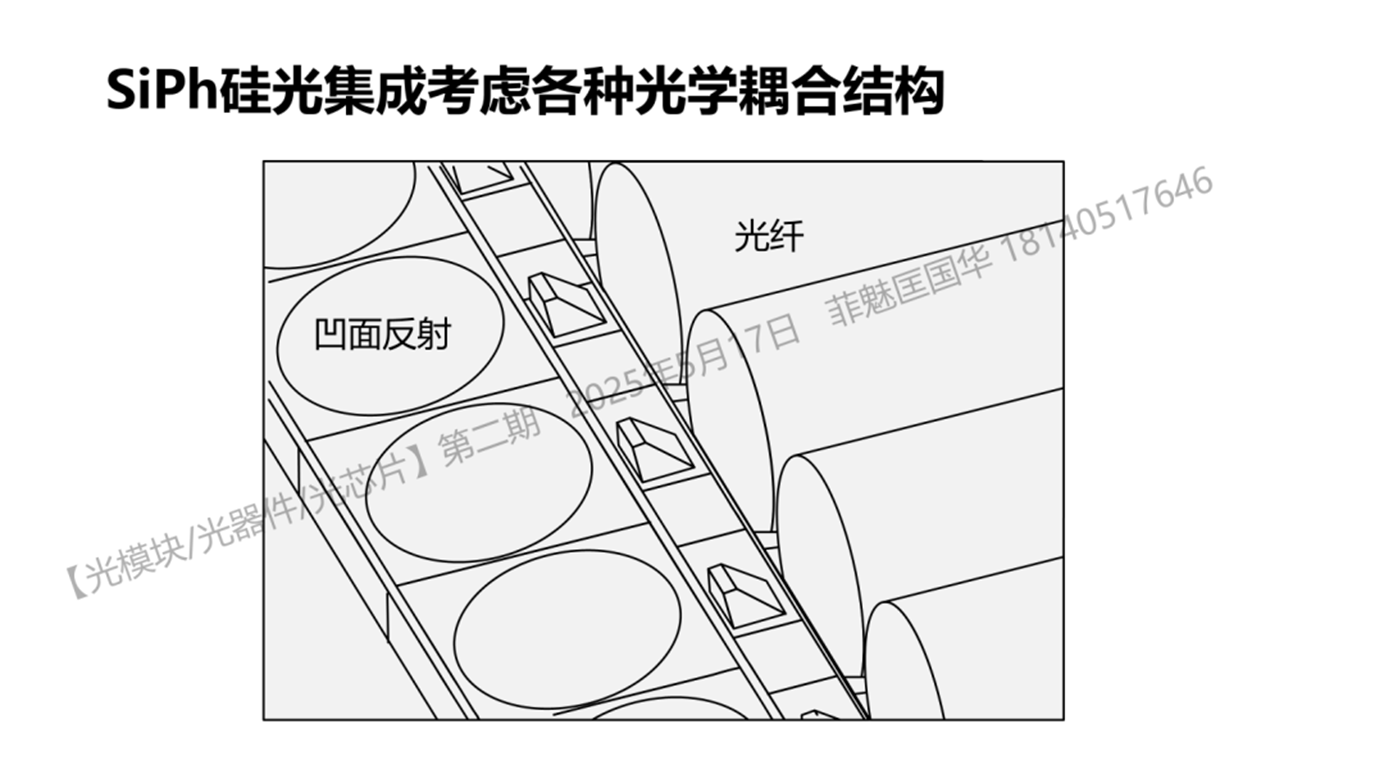

硅光流片工艺外,还有更为繁复多样化的光学耦合设计,以及封装工艺。

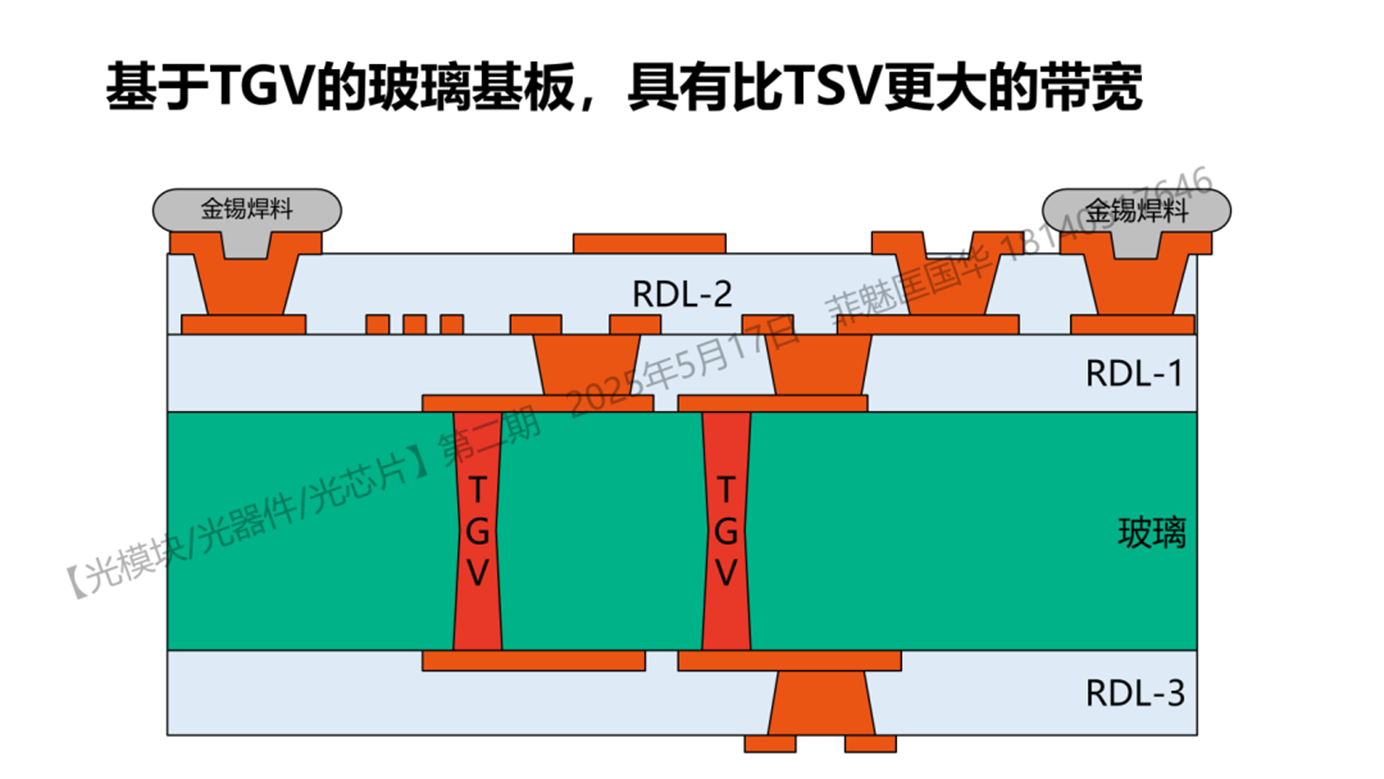

EML有硅基板、陶瓷基板、玻璃基板的封装。

VCSEL有树脂基板,陶瓷基板,玻璃基板的封装。

同样的集成芯片的晶圆级封装,有晶圆级布局树脂局部硅基板,有晶圆级硅基板,也有晶圆级玻璃基板。晶圆级封装考虑在更小的孔径与线宽下实现更高的射频带宽,也就带来更复杂的工艺与可靠性挑战。

略放了几页图,做个引子,周末细聊。