下个月就要CIOE和ECOC了,下半年日子口还挺紧张的。

OFC今年整理了五百多页内容,上周六一天没聊完,今天就扫尾了。惯例做个整理纪要。

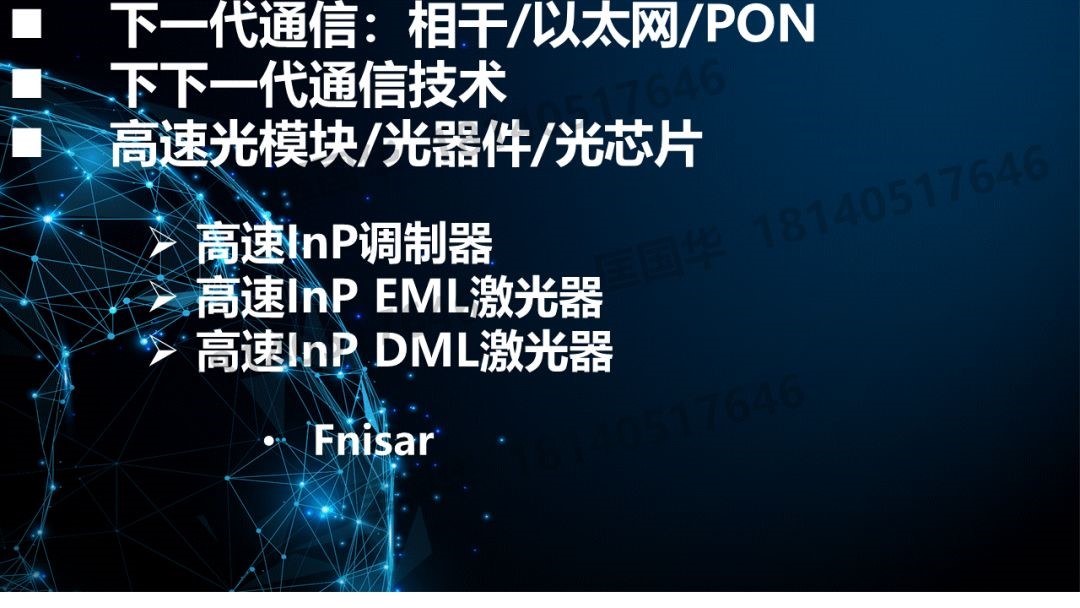

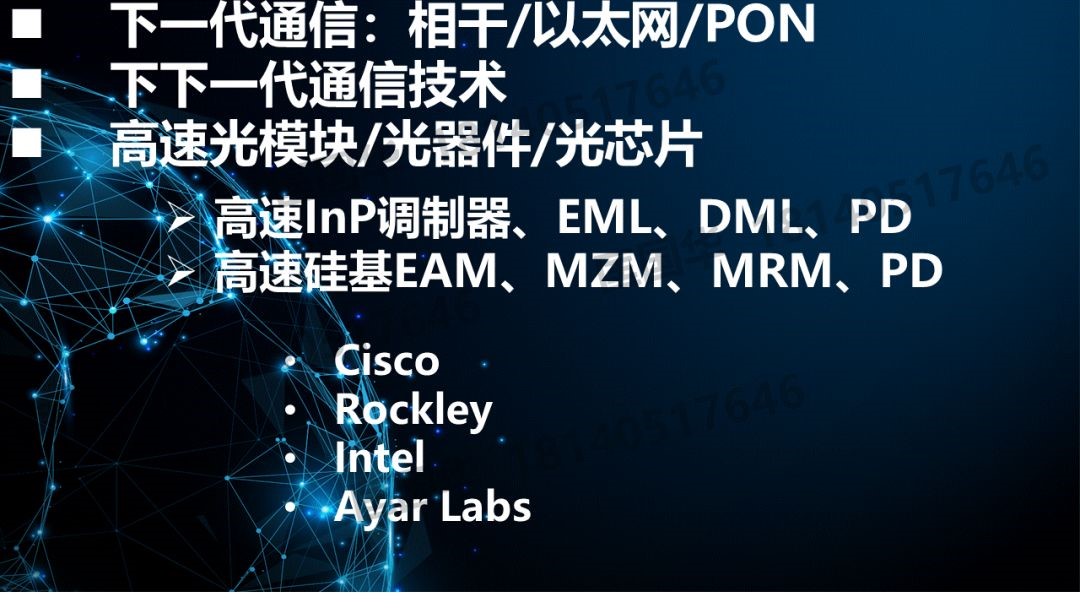

下一代通信技术

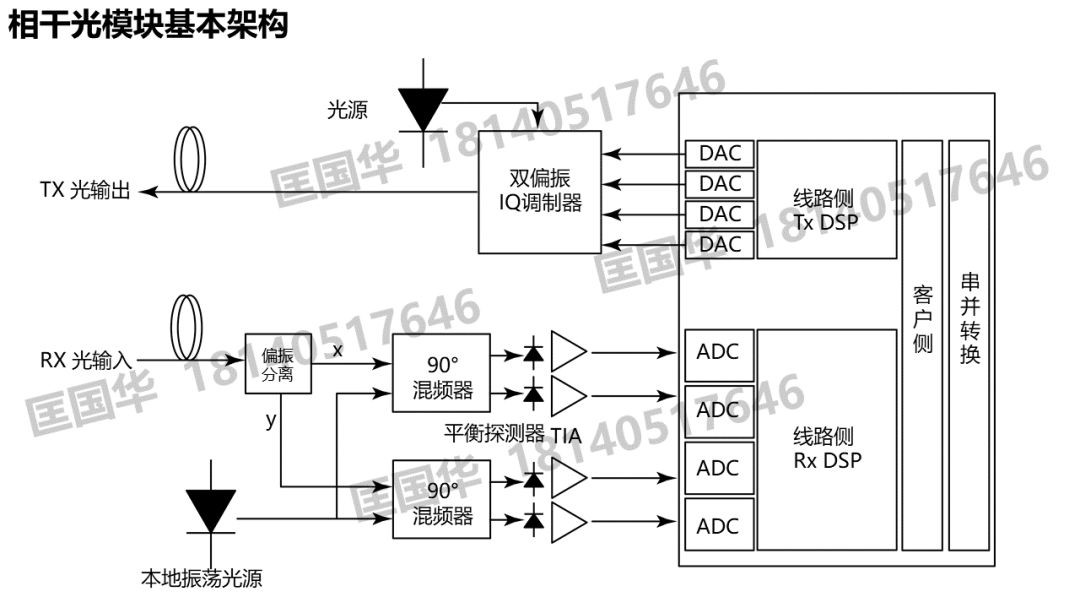

--相干

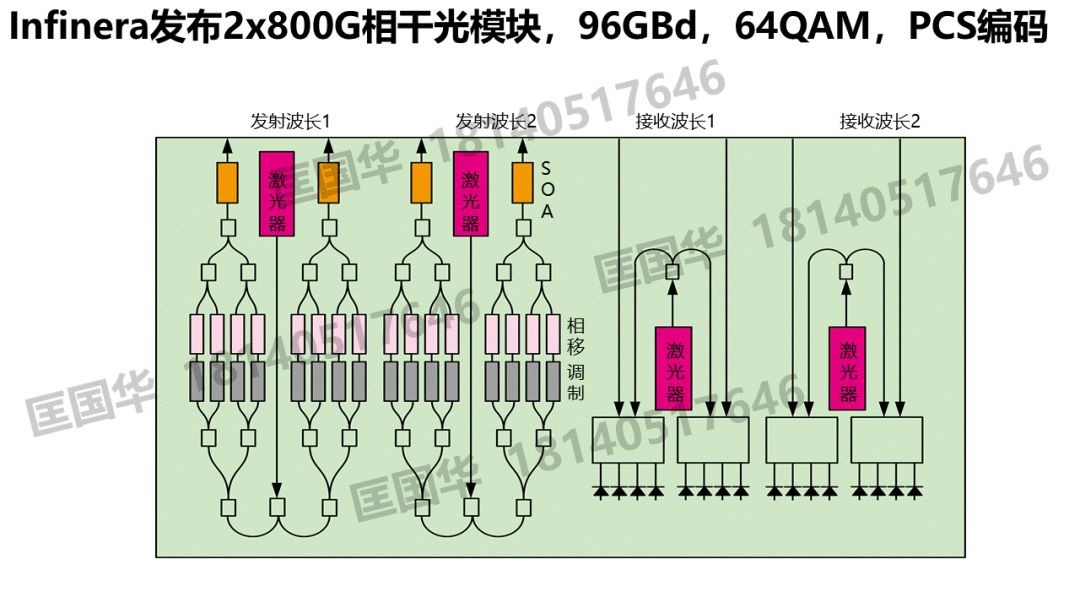

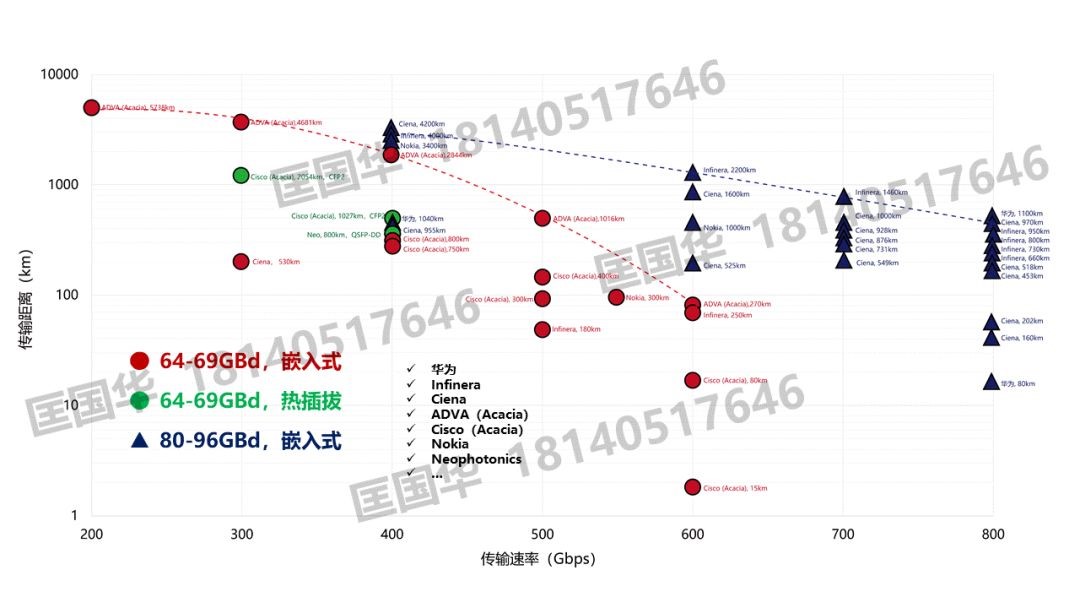

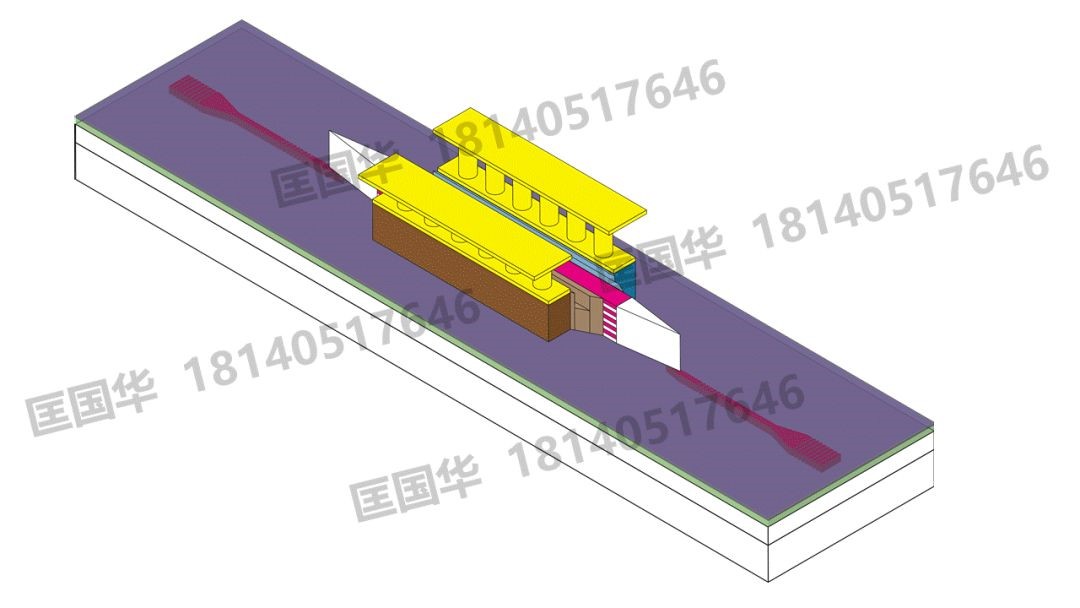

Infinera在2020年年末发布2x800G相干模块,2021年OFC一方面解读他家的相干模块。另外有一个可用于弹性架构的DSP科普讲座。

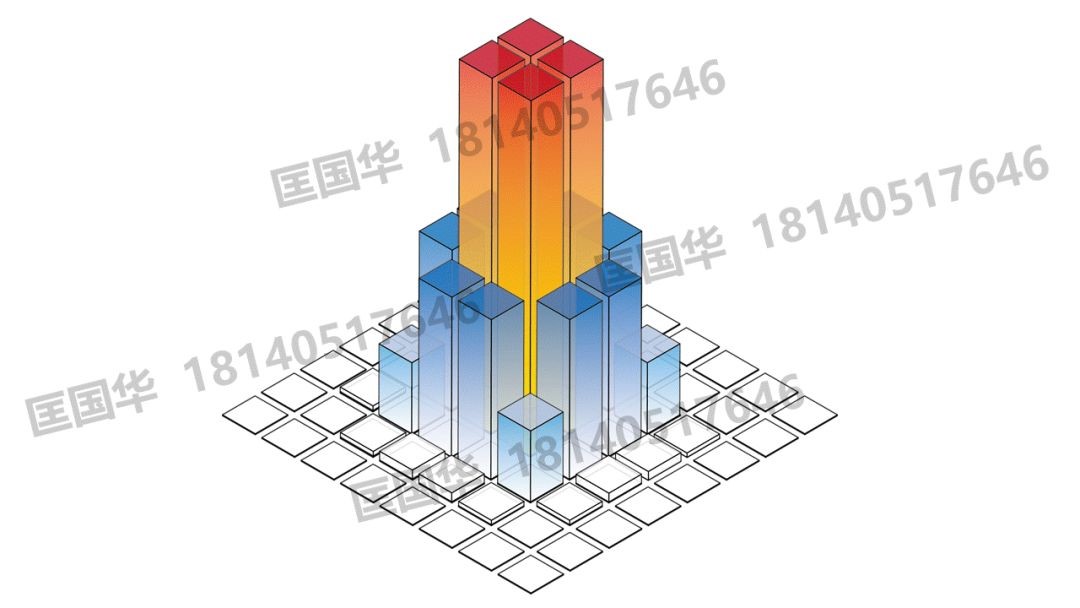

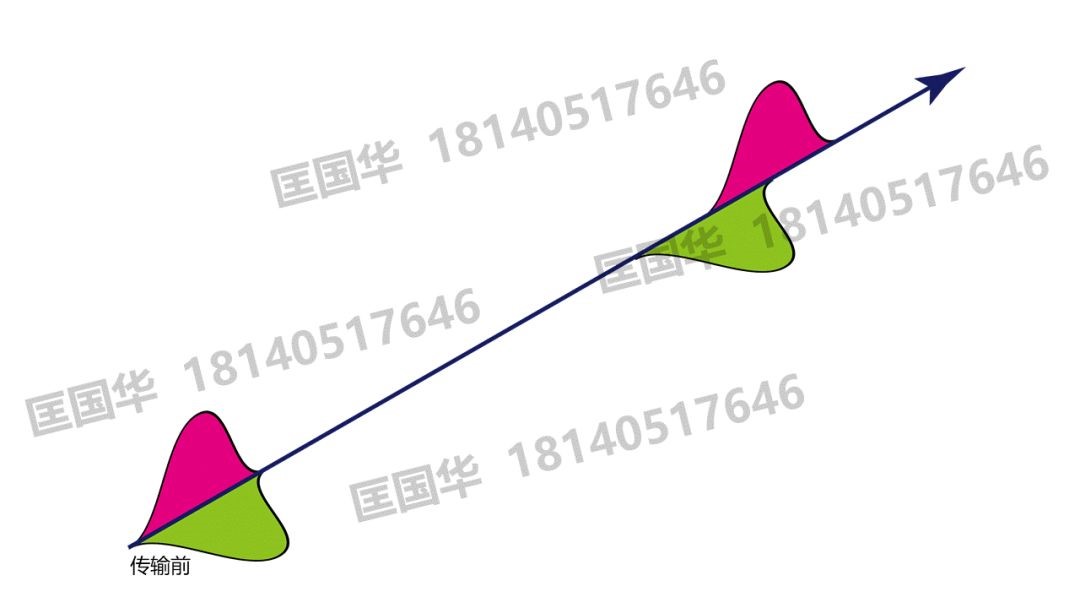

接近香农极限的PCS编码

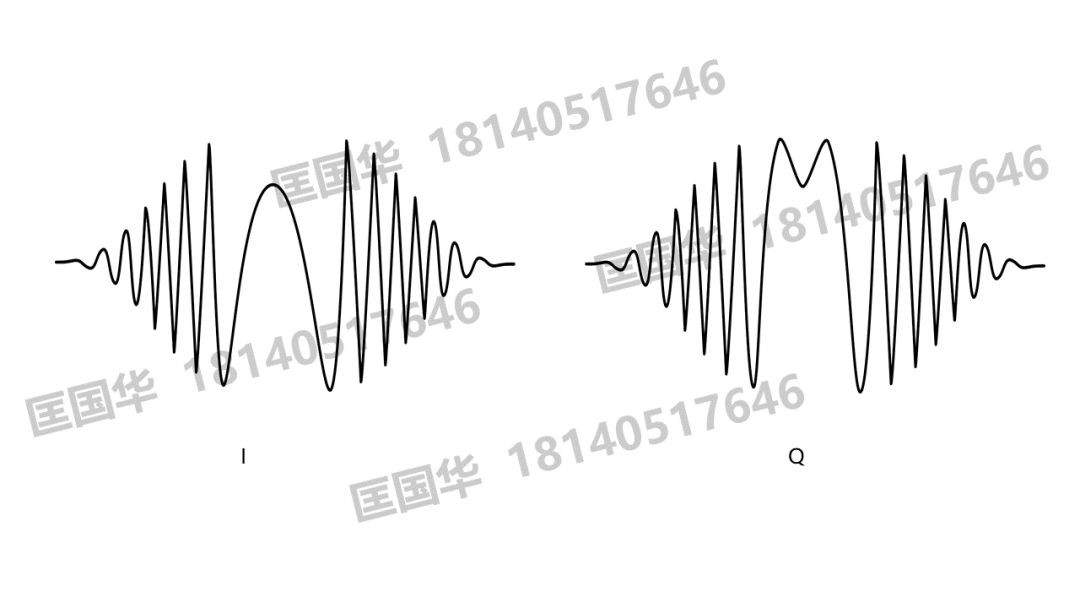

色度色散的处理

偏振模色散处理

整理了一下这些年DSP的进展,速率、格式、带宽、工艺节点以及集成度

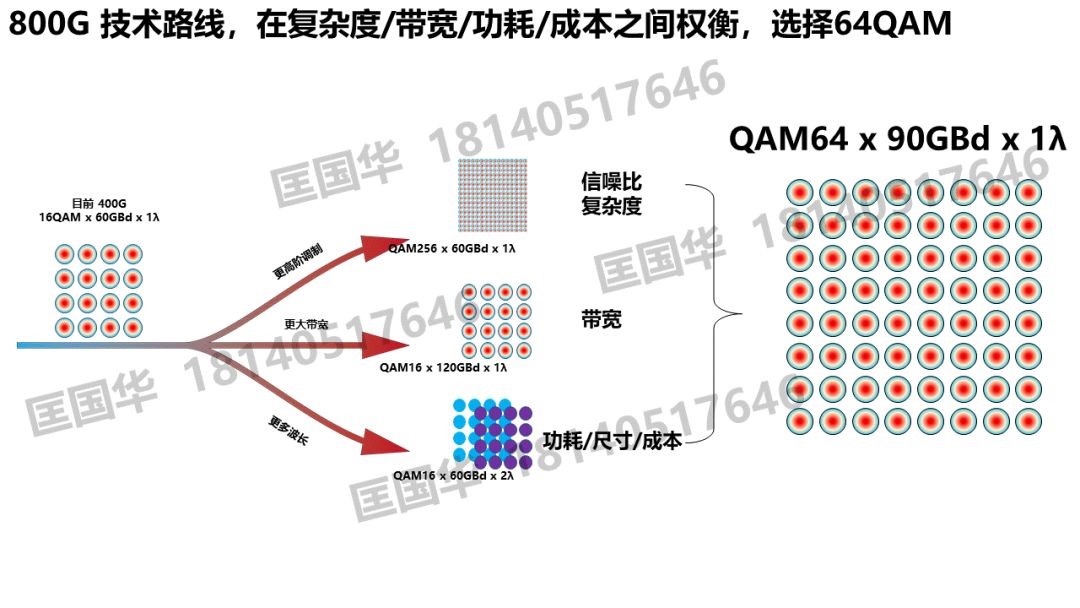

Inphi,有好几个报告,对下一代相干技术,倾向于选择96GBd,QAM64,在下一代以太网224G倾向于选择PAM6

Acacia

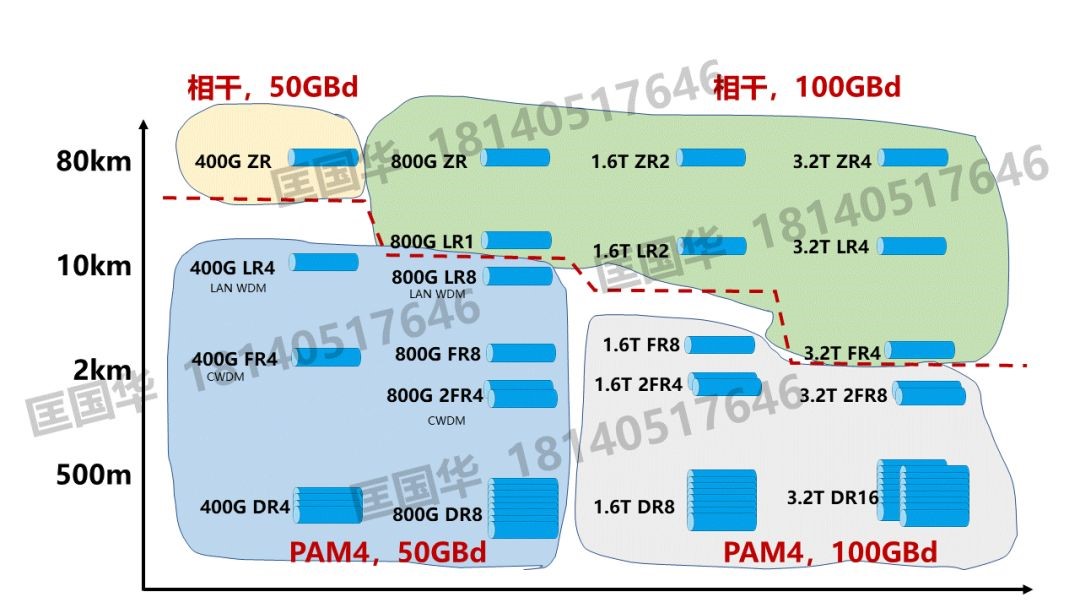

对下一代相干,认为800G/波长可以很长时间,且可以通过不断的迭代波长复用提高通信密度。

在早期封装,以热插拔为主,下沉到LR,后期相干也可以做Co-packaging,且下沉到FR的距离。

新飞通,则整理了这些年主要做相干模块厂家技术汇总表,在未来InP以长距为主,SiP以短距为主,支持相干下沉

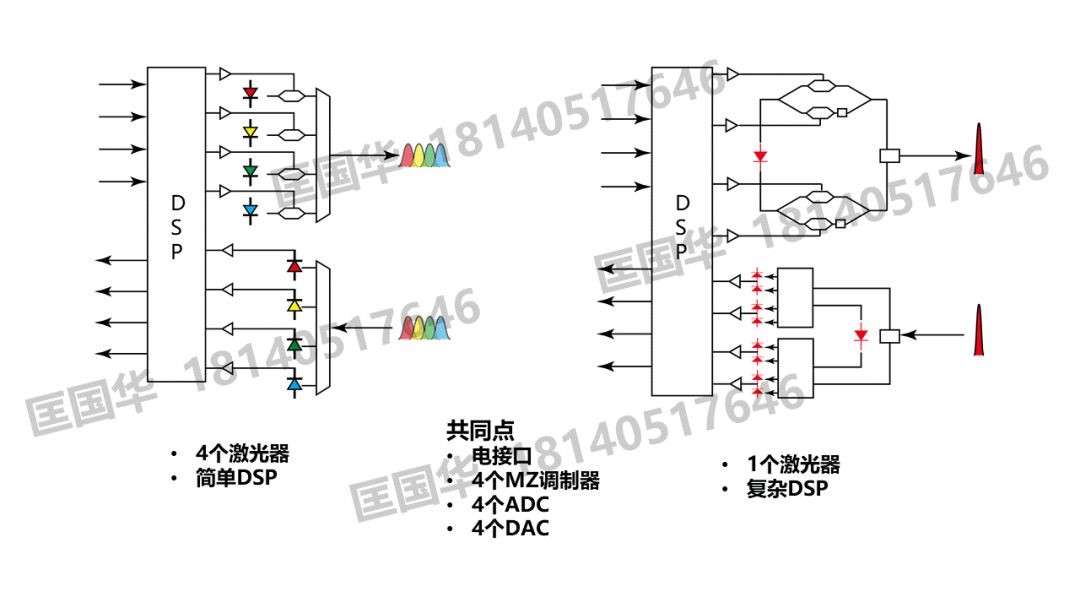

谷歌,分析了这么多年他们部署的前五代光模块的技术特点,在未来的400G之后告诉发展,EML由于微小啁啾而受限,需要MZ调制,对于MZ调制来说,无论相干还是PAM,都有很多共同点,相干更有产业发展的低成本、高密度、高带宽和高信噪比持续优化的优势。谷歌倾向于相干,只不过和前几个厂家相比,不太喜欢Co-packaging的相干而已。

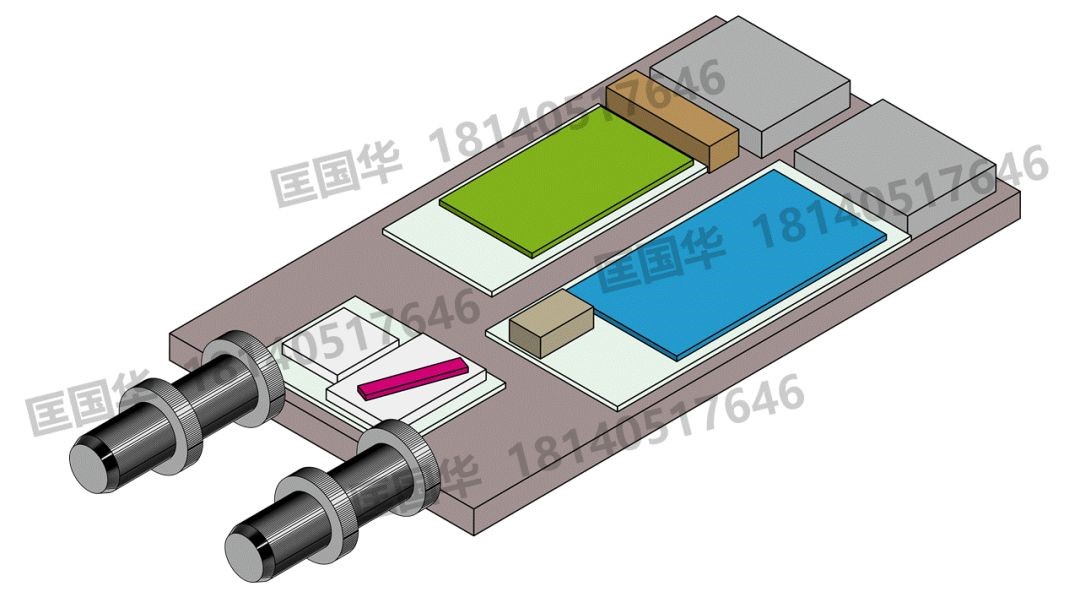

古河,展望了他家从十年前的嵌入式相干,5x7吋,到4

x5吋,再到热插拔一路小型化的结构变化,深度分析可用于QDD的热插拔模块的微环InP可调谐小型激光器,PLC的锁波装置,IQ调制器,以及探测器阵列封装,PLC的相干封装....

诺基亚,收购Elenion,也回顾了他家第一二三代的相干器件的主要功能。

华为和华南师范,用于低成本同源相干Bidi方案的偏振跟踪与控制器,无需TEC,用普通DFB,放弃高成本的窄线宽激光器,用铌酸锂薄膜来做偏振旋转的跟踪控制

Intel,在OFC上的报告很多,对下一代数据中心的演变,观点是用集成激光器的方案,单通道100G,满足色散受限的长距传输,多通道复用,下一代具备成本优势。与其他几家推动CEI-224G的思路不同。

复盘PAM4的技术成败

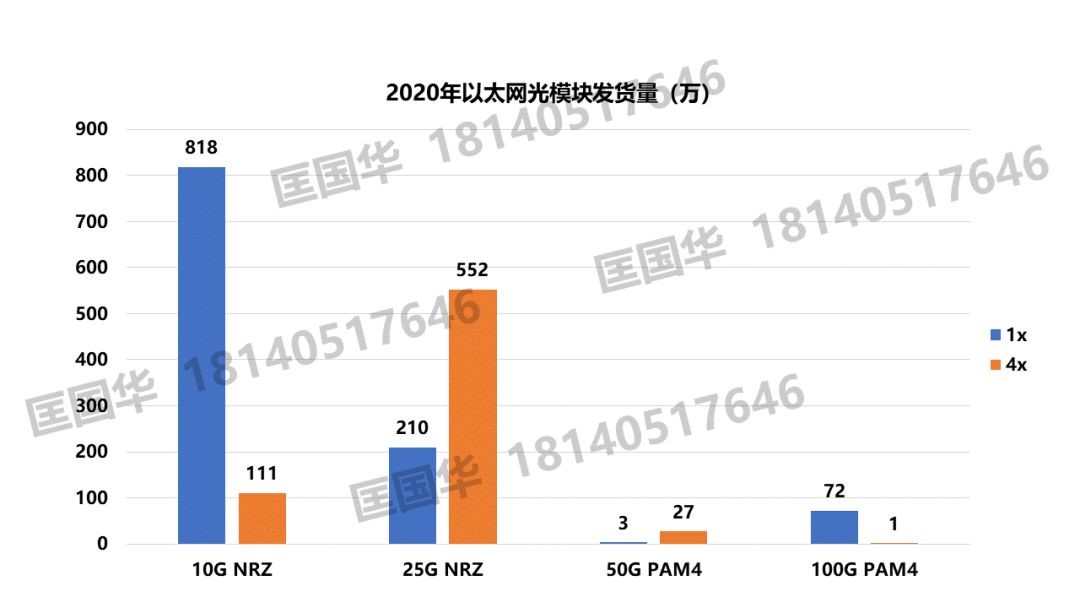

Finisar,Inphi、Google、Infinera等厂一起讨论的已经部署了数百万只的PAM4光模块,看起来不算成功。

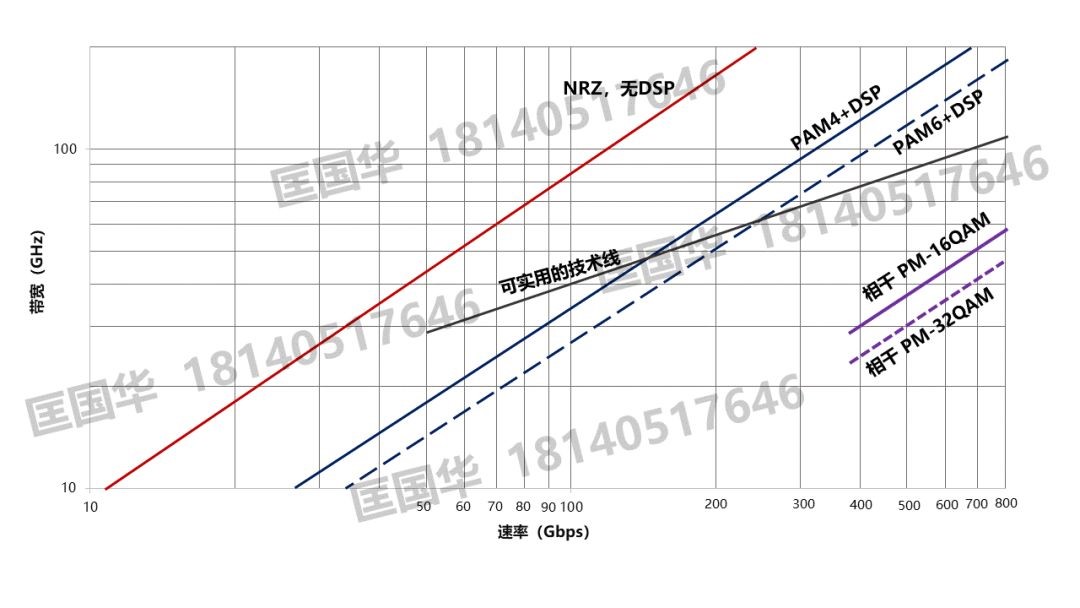

原因,PAM4需要付出4.8dB的信噪比编码代价,且传输代价增大,当初是为了换取低带宽。五年过去了,器件的带宽已经提升和发展,而当初的PAM4的代价却是无法抹去的

建议方式一,用高带宽的NRZ,直接替代PAM4

建议方式二,用几个低带宽的NRZ,WDM方式,替代PAM4

建议方式三,用相干替代PAM4,也就是更早一些相干下沉。

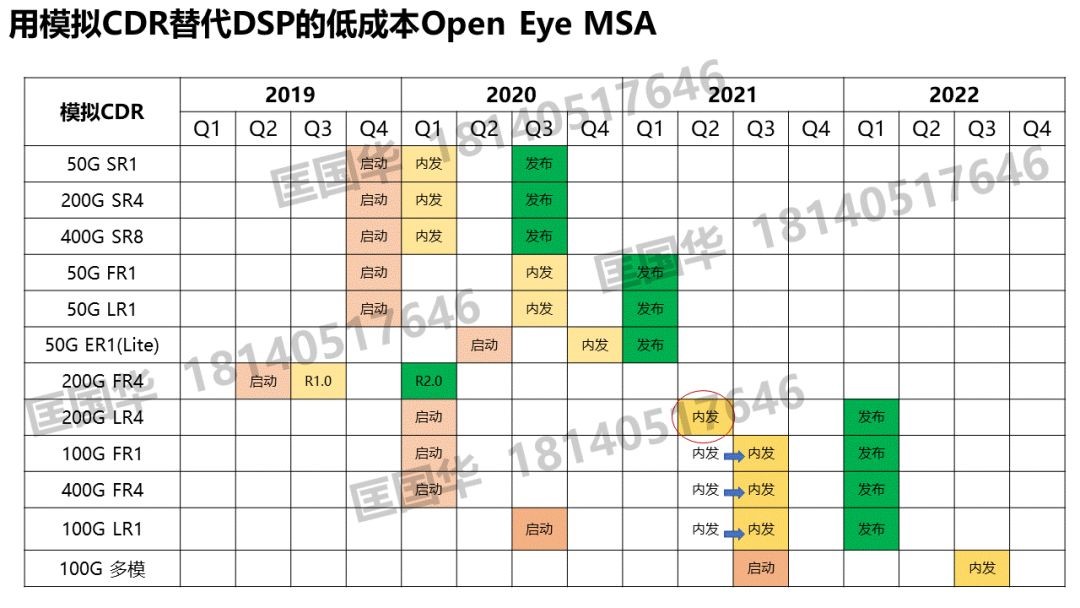

复盘PAM4的部署,还有一个折衷方案,就是降低PAM4用的DSP的功耗和成本,也就是所谓的模拟CDR来替代数字DSP,这是以Semtech、Macom为主推动的。

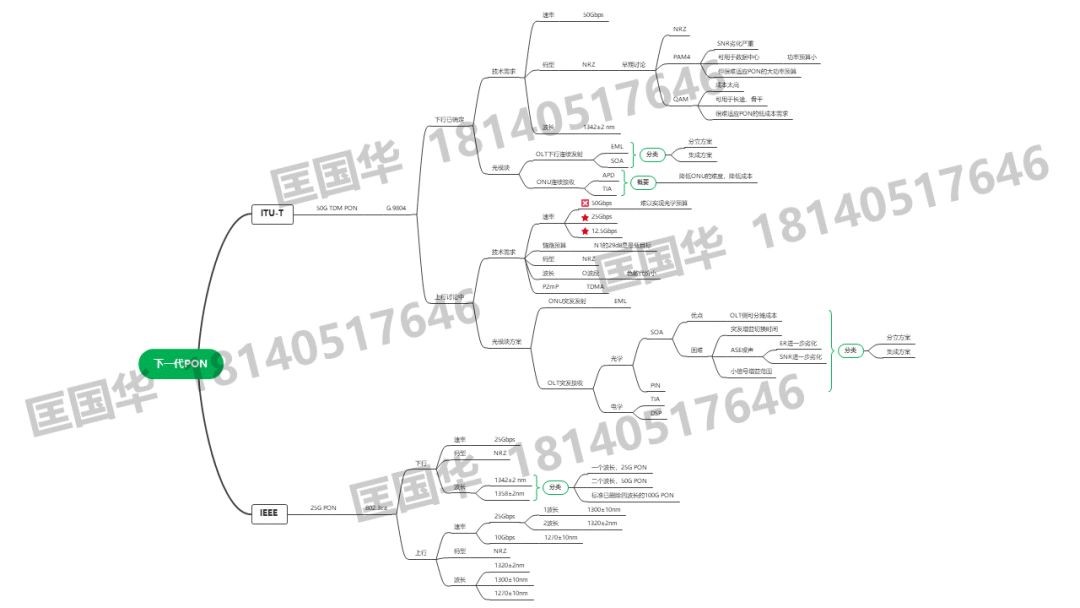

下一代PON

25G EPON,以及50G EPON,在2020年已确定并发布。

50G TDM PON,下行方案已经确定,上行方案讨论中,预计近几个月可确定。

脑图写了波长规划,发射端和接收端处理

总的思路,尽量产业链共享,波长规划基本上能看出来走向

PON的链路预算很大,OLT的发射和接收,基本要确定加光放大器,华为去年发布的1342nm EML,用外置SOA,NTT发布1358nm 集成SOA的EML激光器芯片,诺基亚评估SOA的突发接收的各项参数,华为预定的集成SOA的探测器,等等,研究在不断进展中

再往下数,就是更远的技术探讨了。

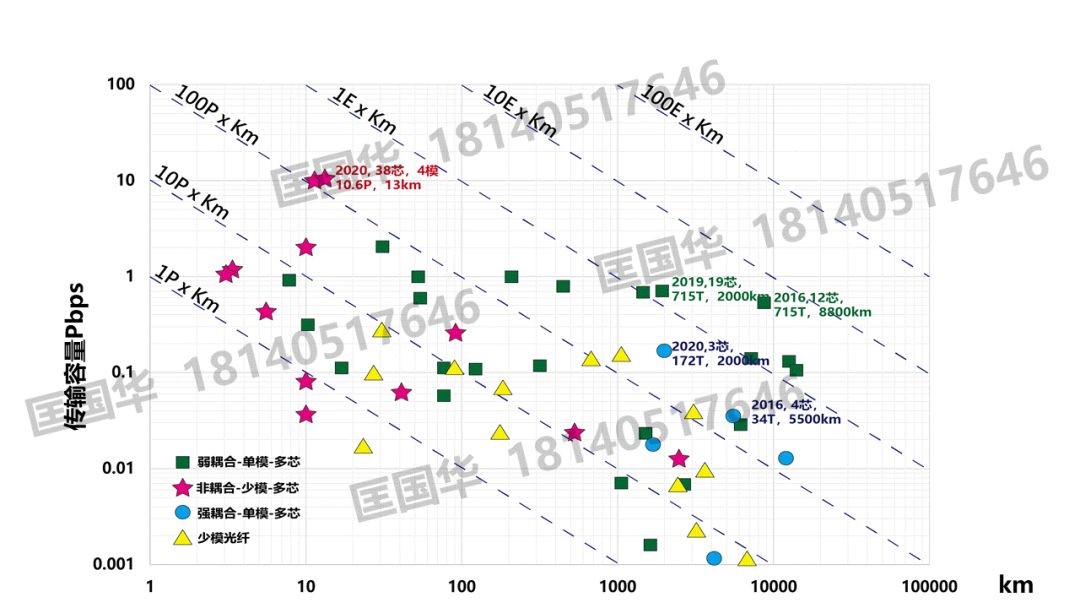

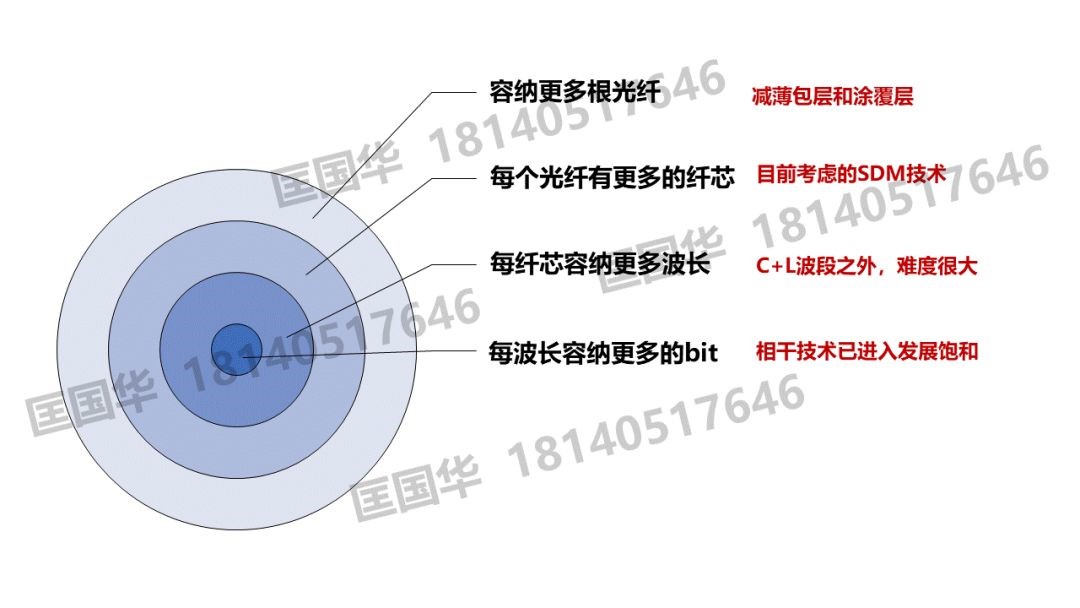

SDM,空分复用,紧耦合与非耦合,串扰、色散等等,今年OFC有科普性包括。标准已启动立项。

康宁,提出在这一代的相干,以及下一代的SDM之间,可以通过减包层和减涂覆层,达到光缆信息容量提升。他们今年也做了很多实验和数据。

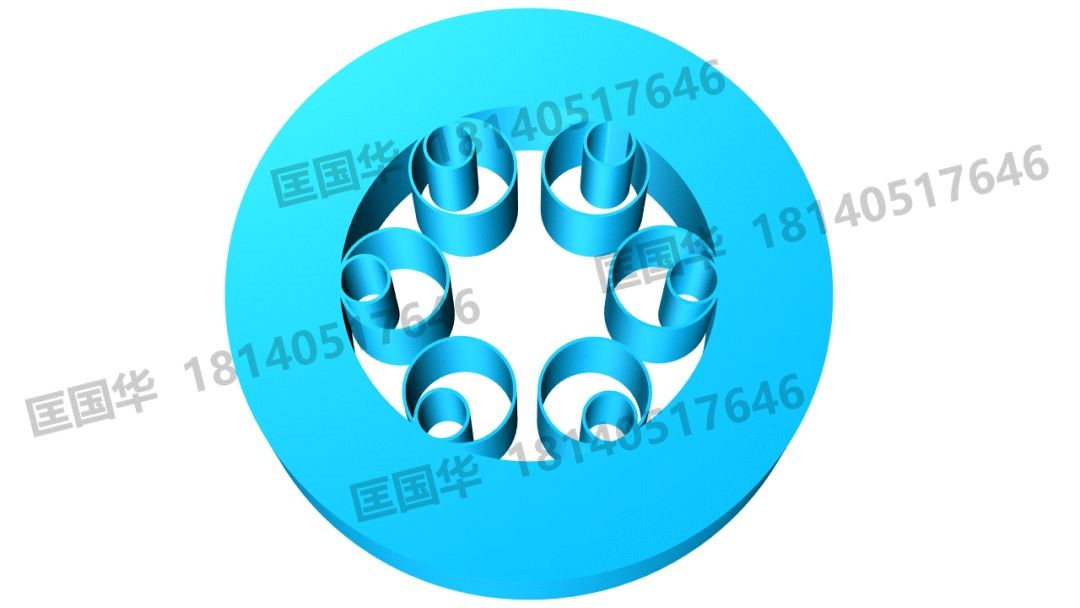

空心光纤,主要是南安普顿在做,这几年的OFC,损耗越来越低,去年的反谐振无节点的设计,用的是六个套管,今年是五个,损耗更小一些,越来越接近目前的玻璃光纤的损耗值了,空心光纤的短时延就是个天大的优势。

上面的是通信技术发展,各家的看法和观点

下面是光模块、光器件、光芯片的新方案

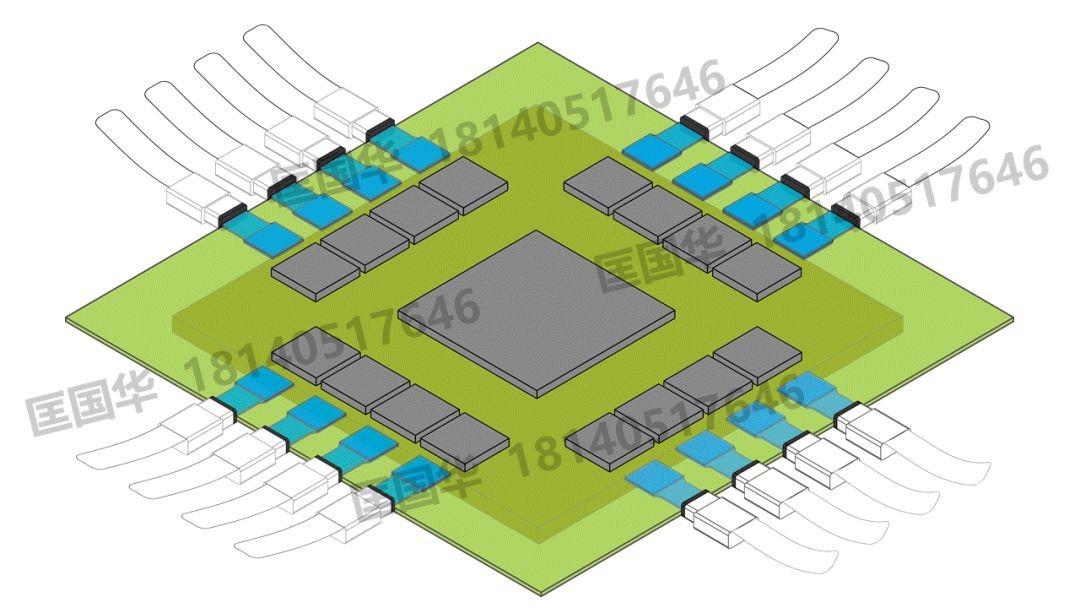

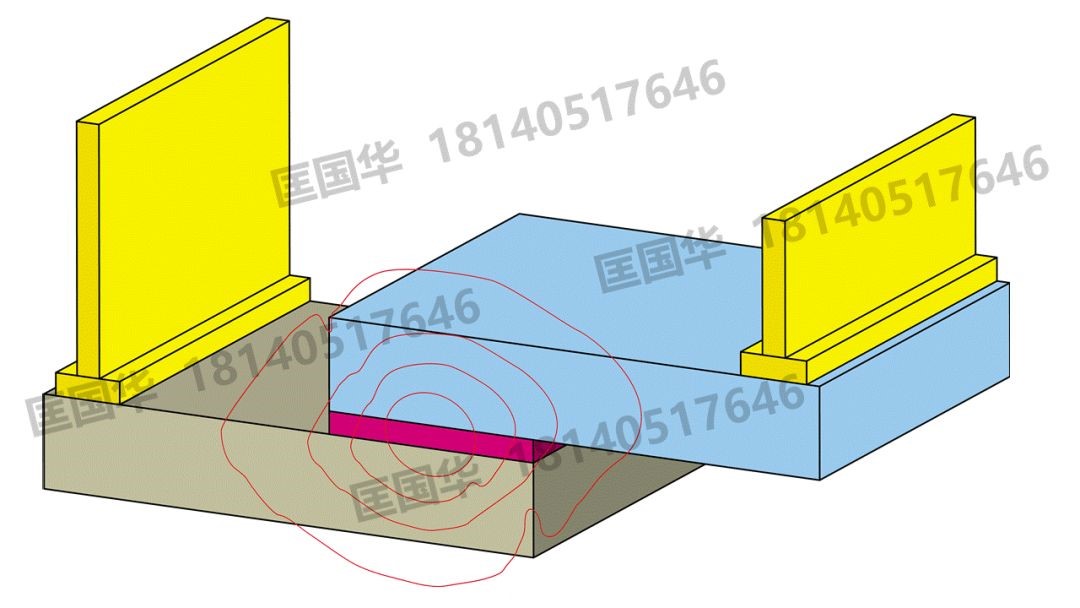

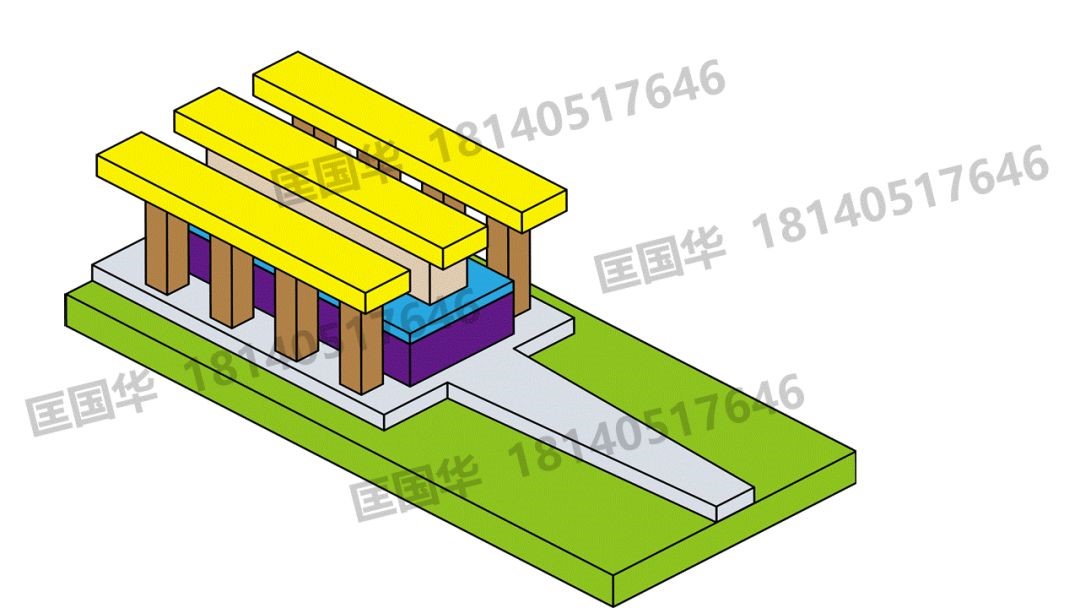

先看Co-packaging的,

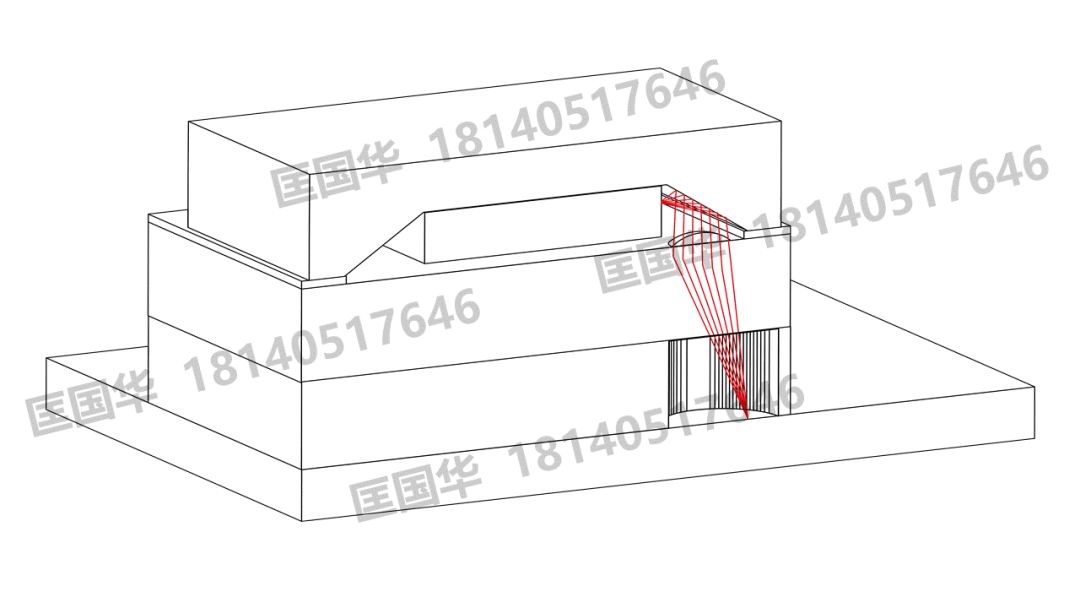

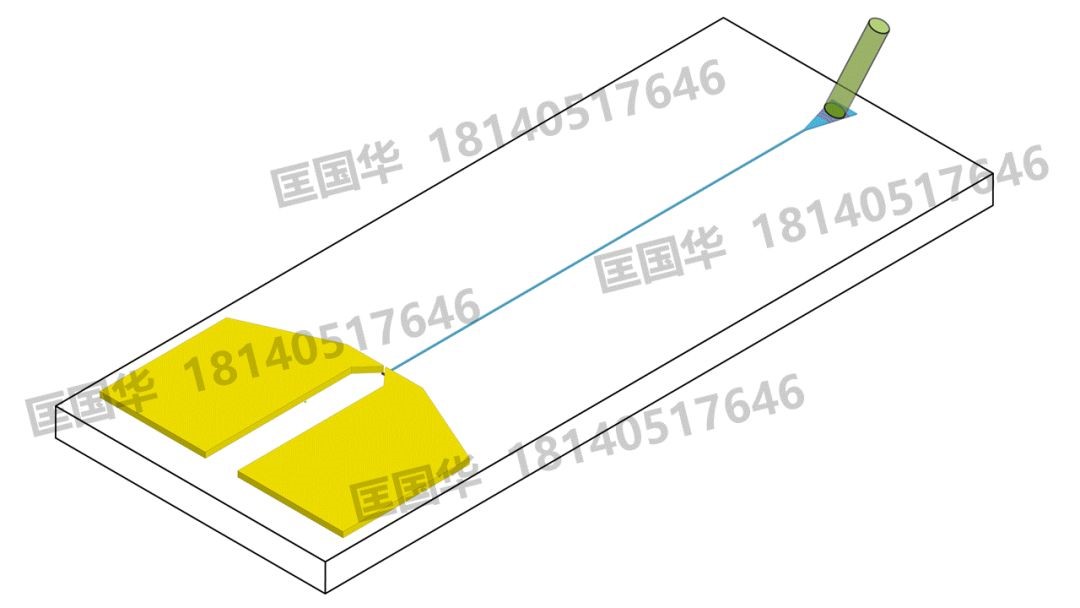

康宁的玻璃封装CPO

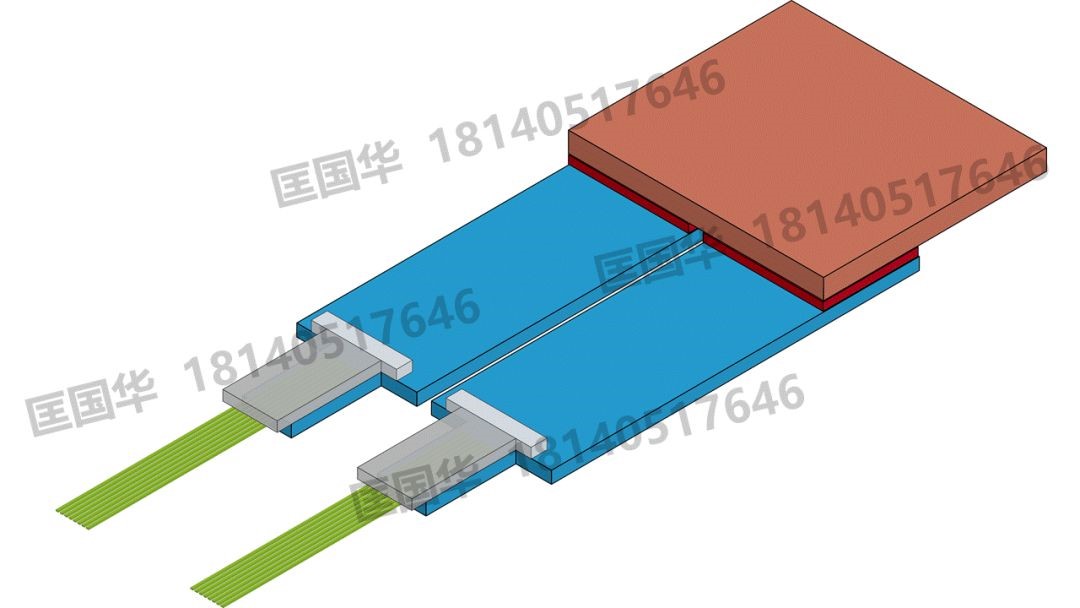

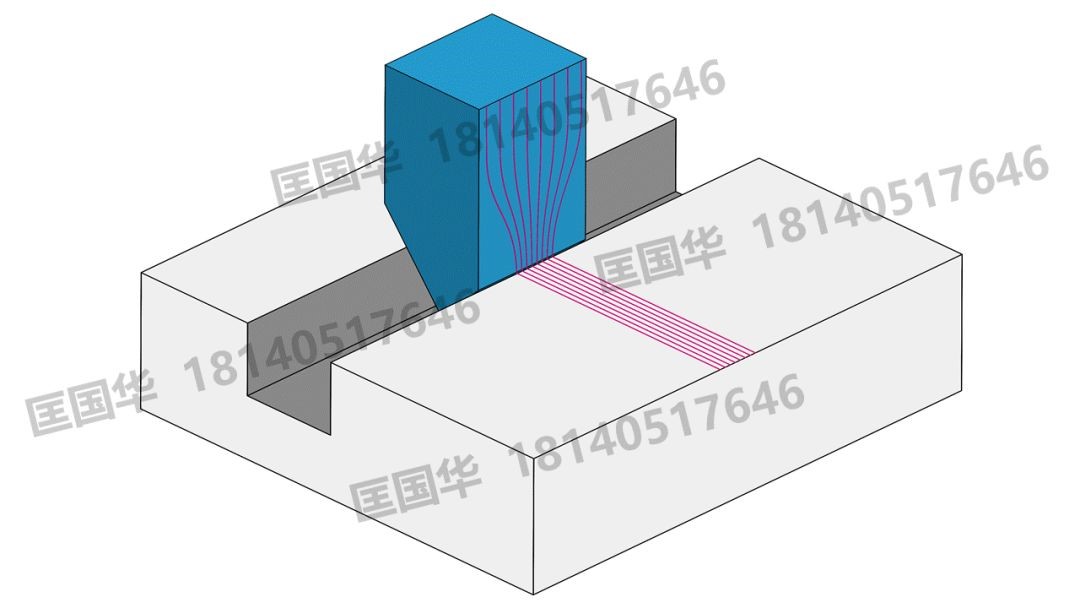

玻璃同时部署电信号扇入扇出,光信号扇入扇出,电信号的话不会像硅TSV有寄生电容,光波导用银离子交换成型。光引擎通过倏逝波耦合到玻璃基板,扇出后,通过倏逝波耦合过渡接口板,与光纤对接。

劣势是,玻璃的高温性能,对光学通道的影响。

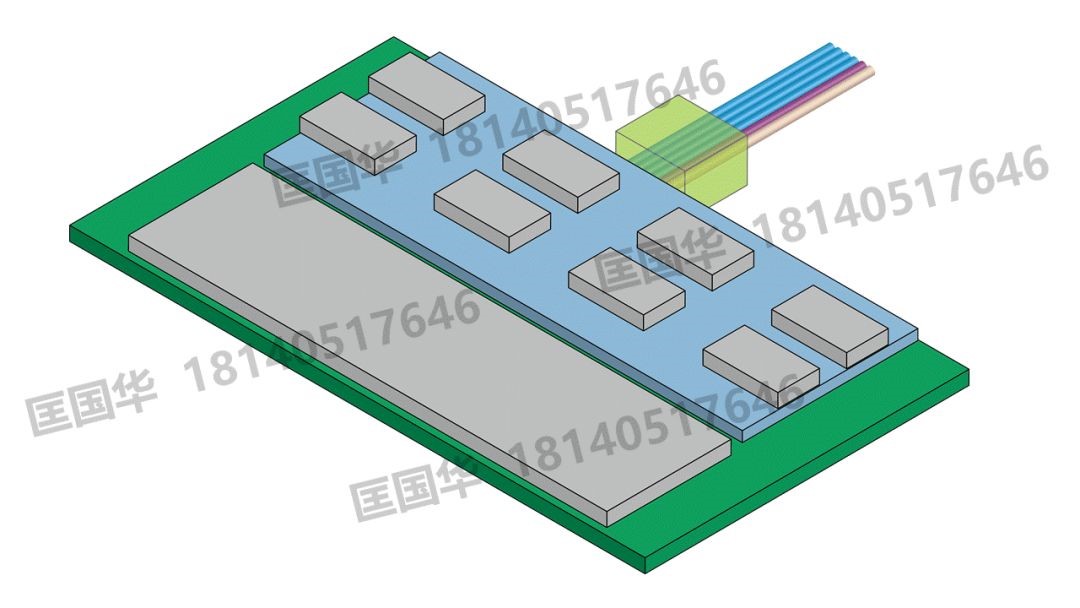

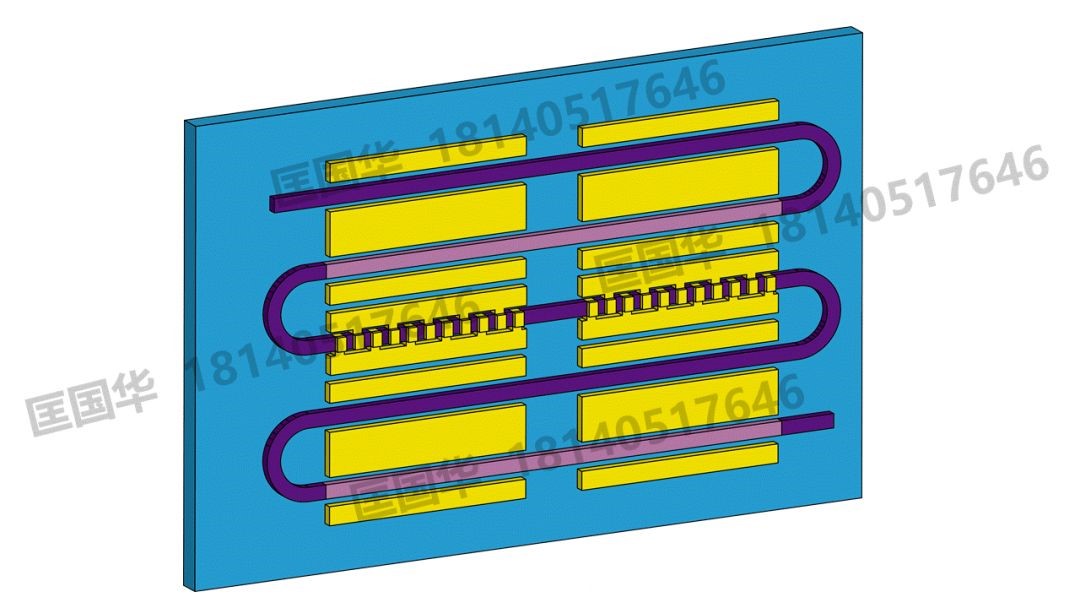

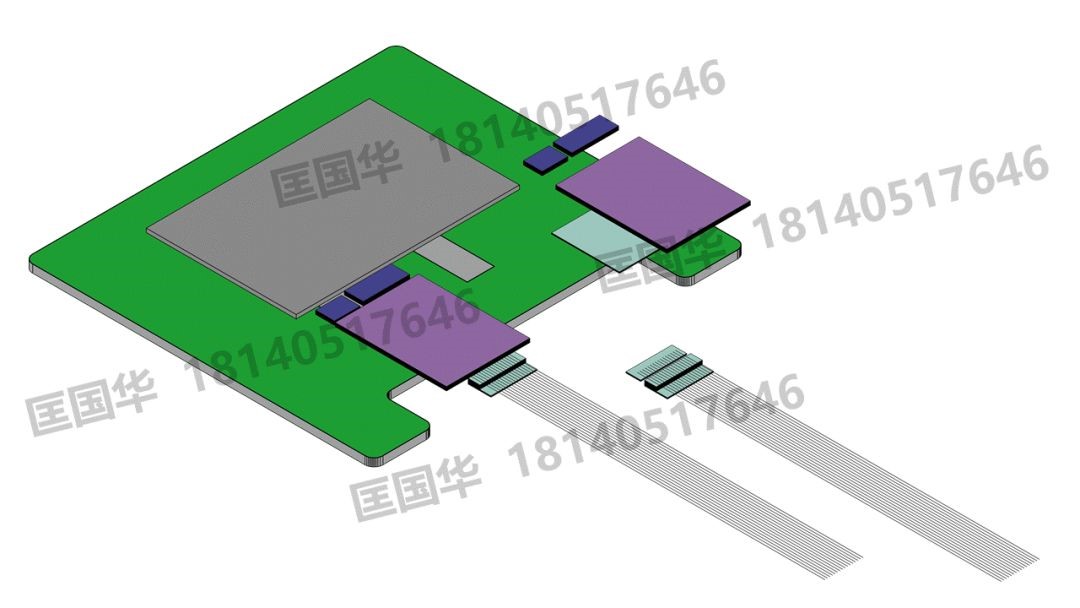

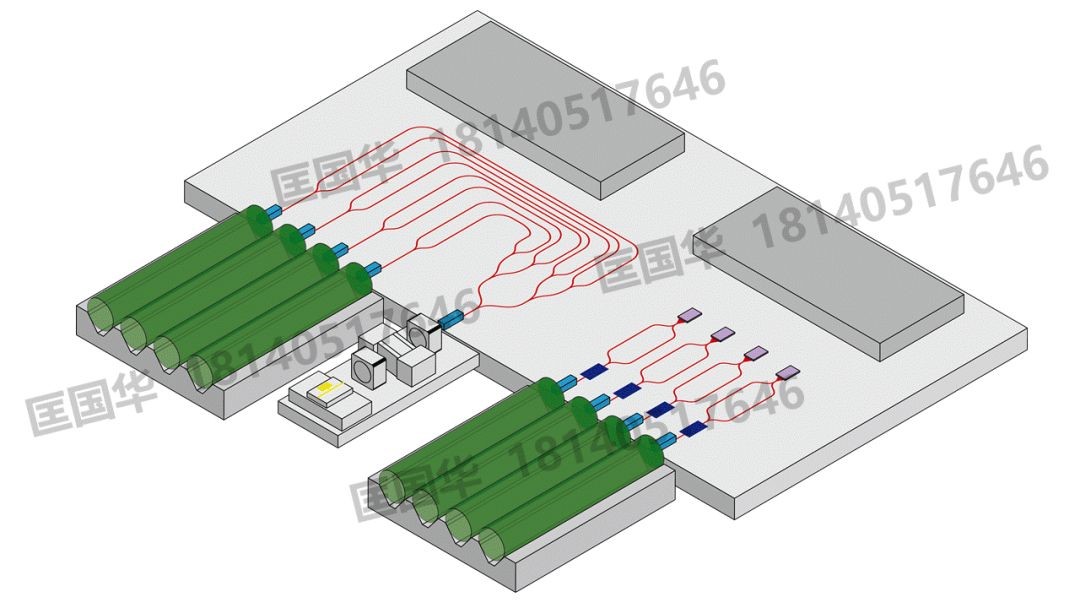

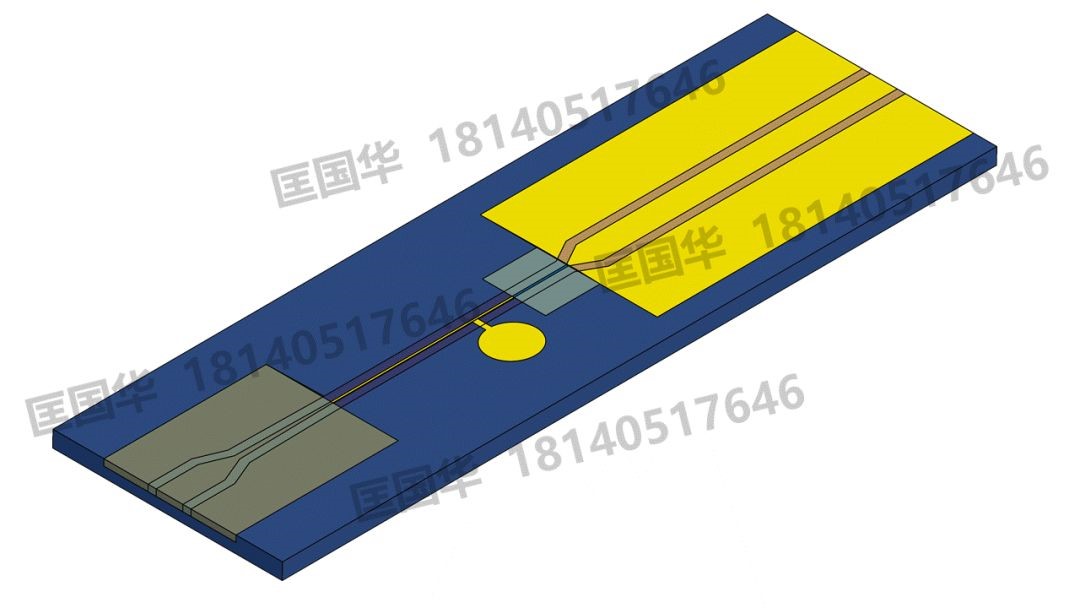

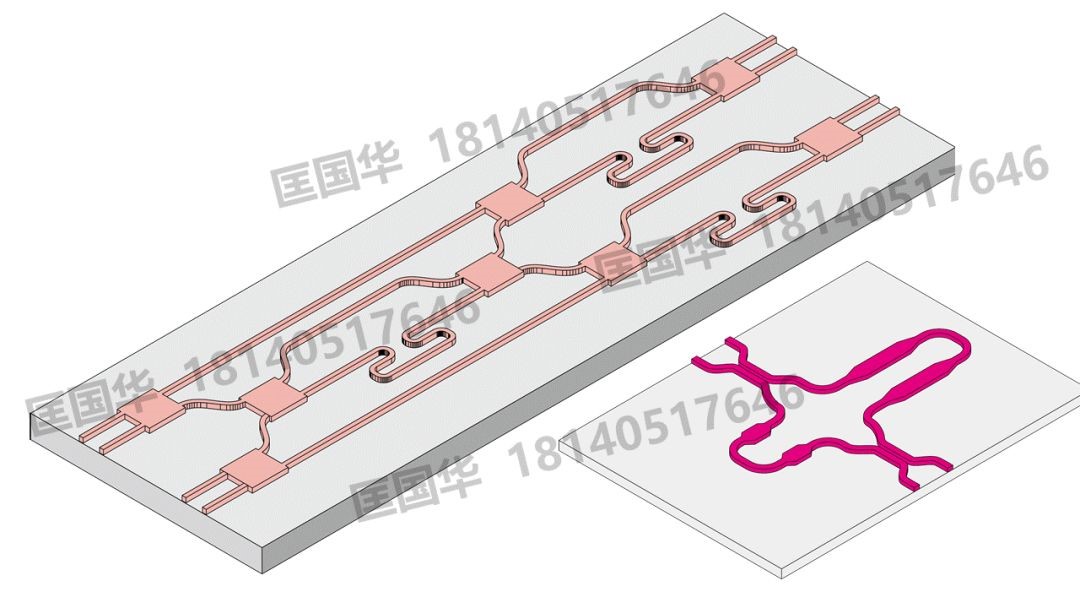

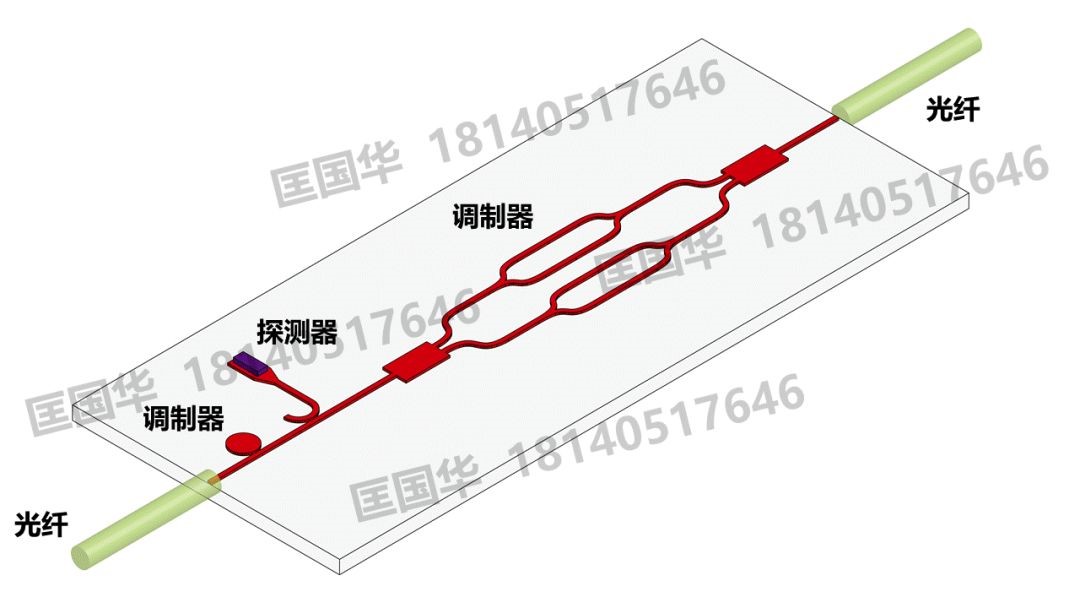

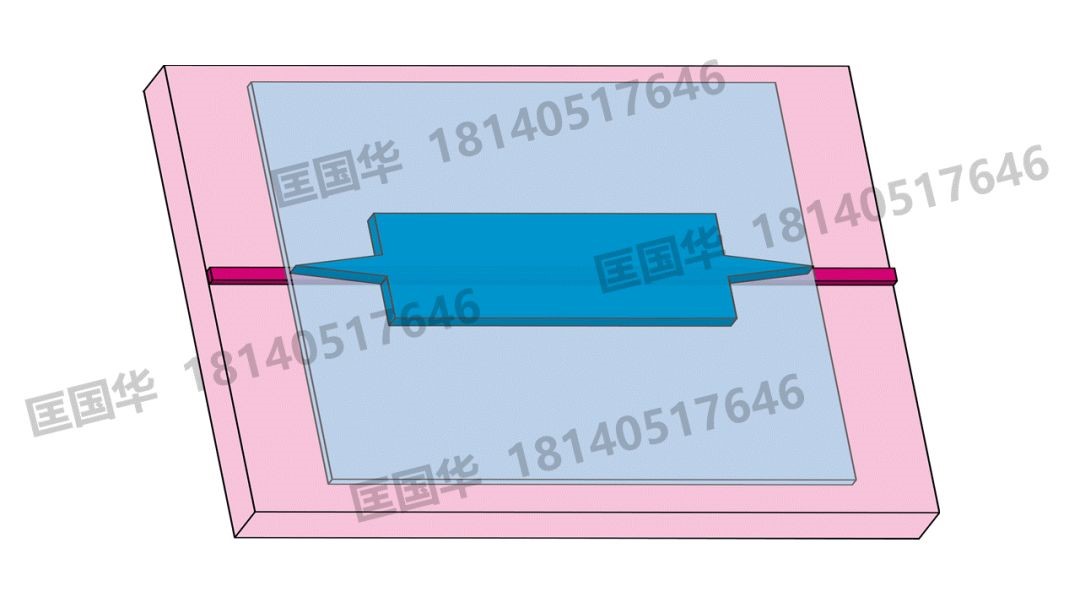

Finisar,给出了三个递进型方案,热插拔可以支撑一代到两代,COBO的COG玻璃封装,还能做过渡,再再来,就是Co-packaging,我们看了他家的COG工艺流程,和CPO的基本流程。以及3.2T基于二氧化硅的偏振不敏感的PLC Demuxh和64个探测器阵列的封装与耦合形式。

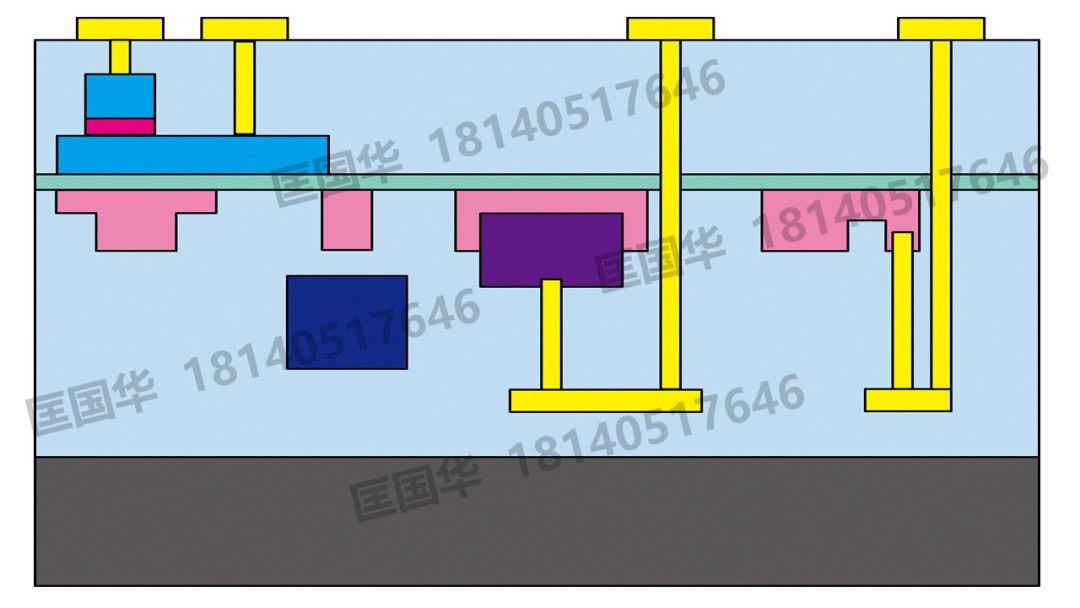

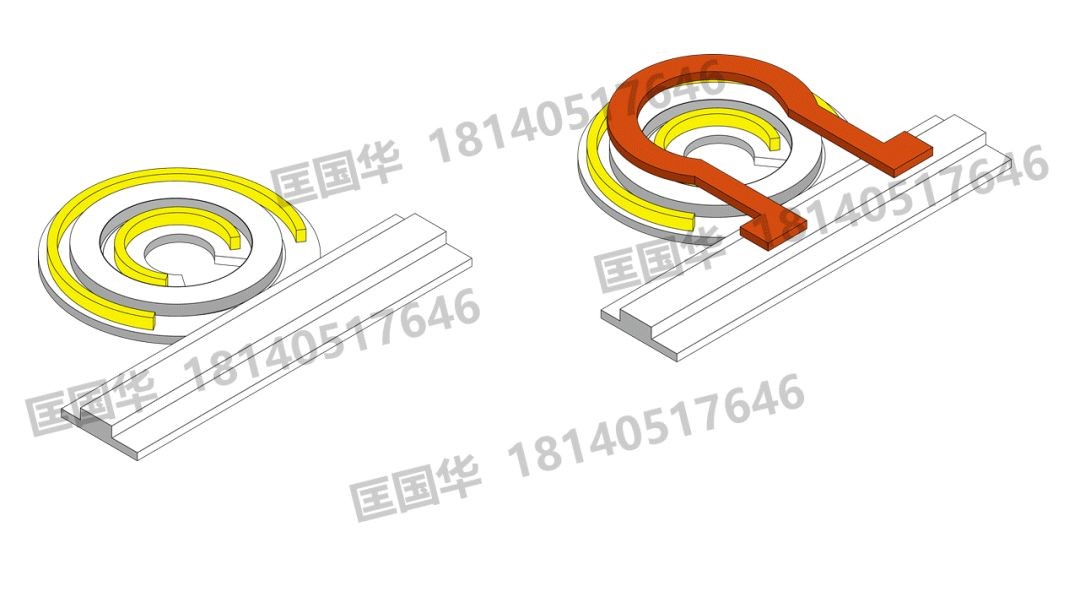

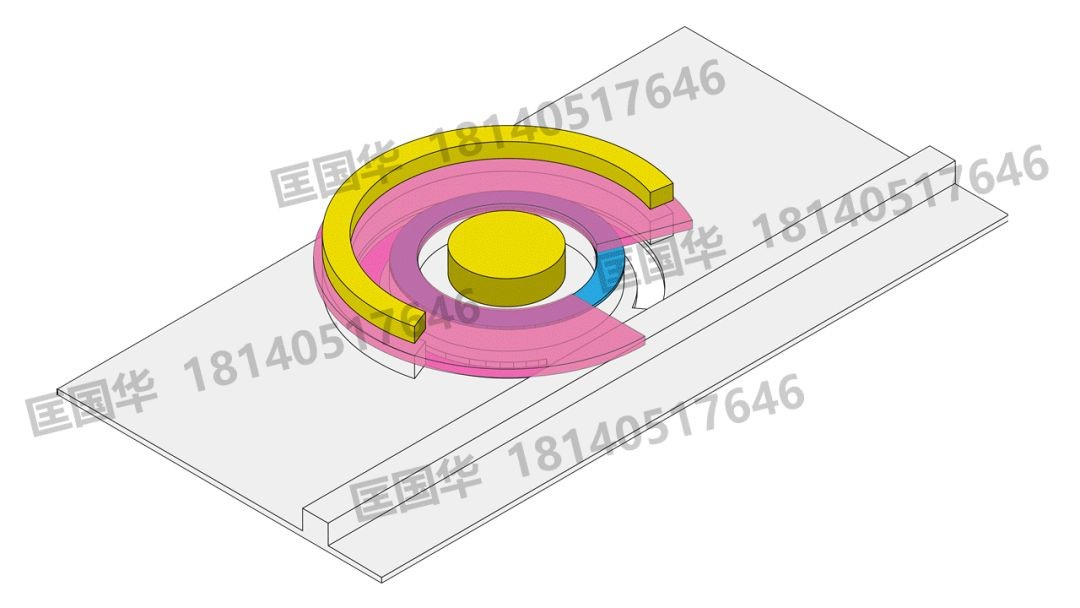

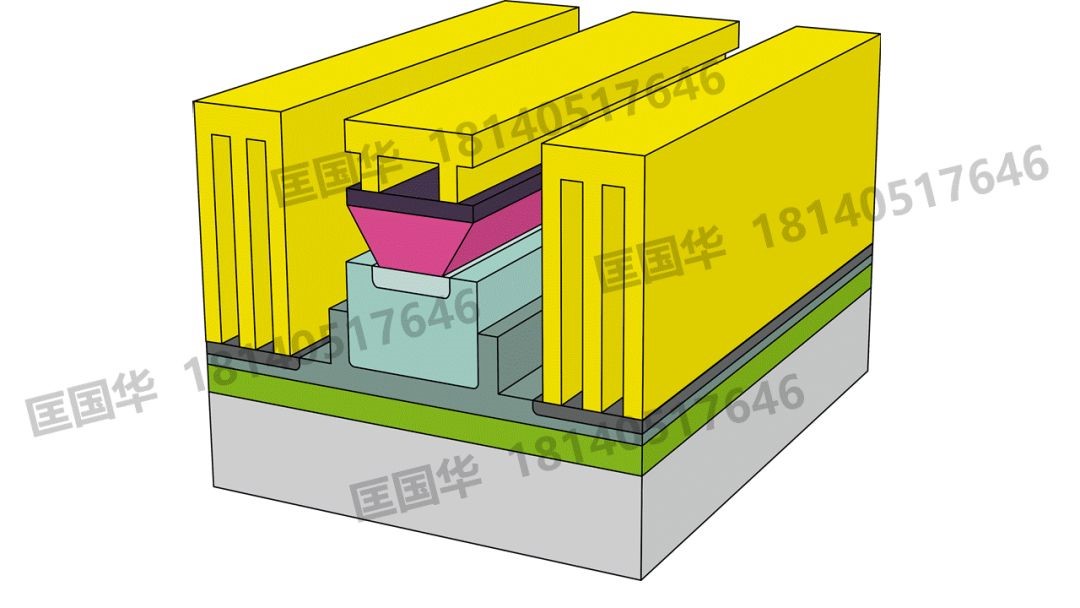

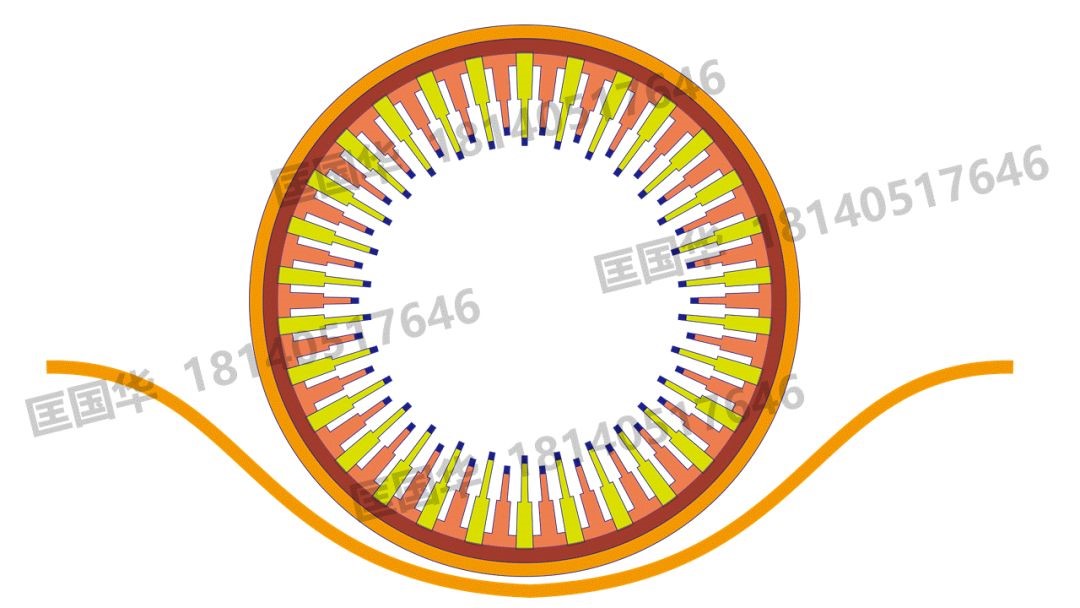

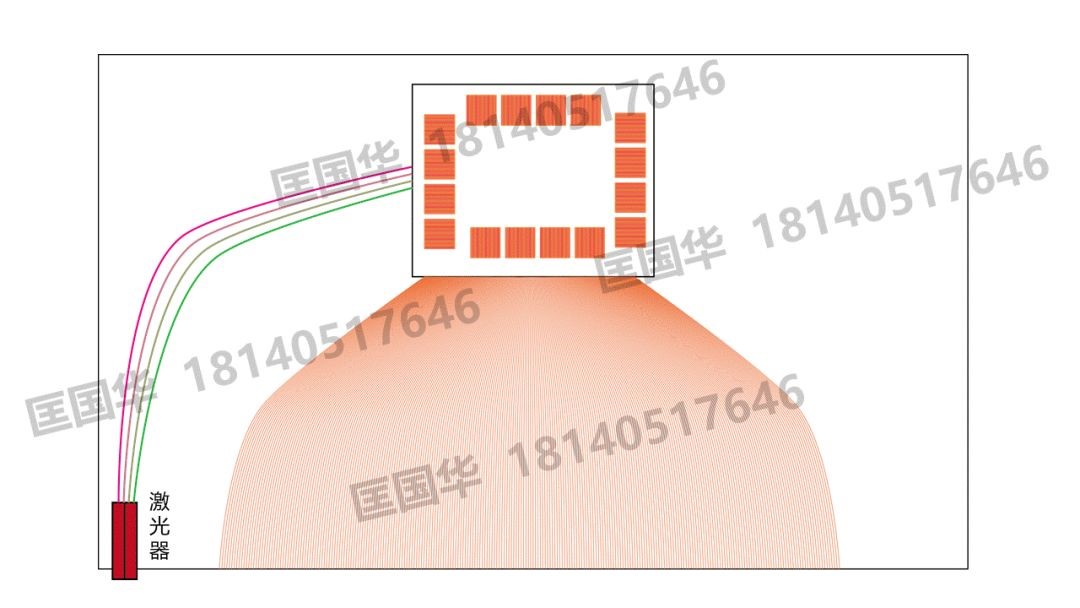

Intel的co-packaging,今年有三个,热插拔有一个,非常热闹。热插拔方案用MZ的调制器,集成激光器的CPO方案用微环调制器,还有一个8T的CPO,用的是Ayar LAbs的回音壁功能的无源微环调制器,以及0偏压的微环辐轮式探测器。这个方案聊的时间长。

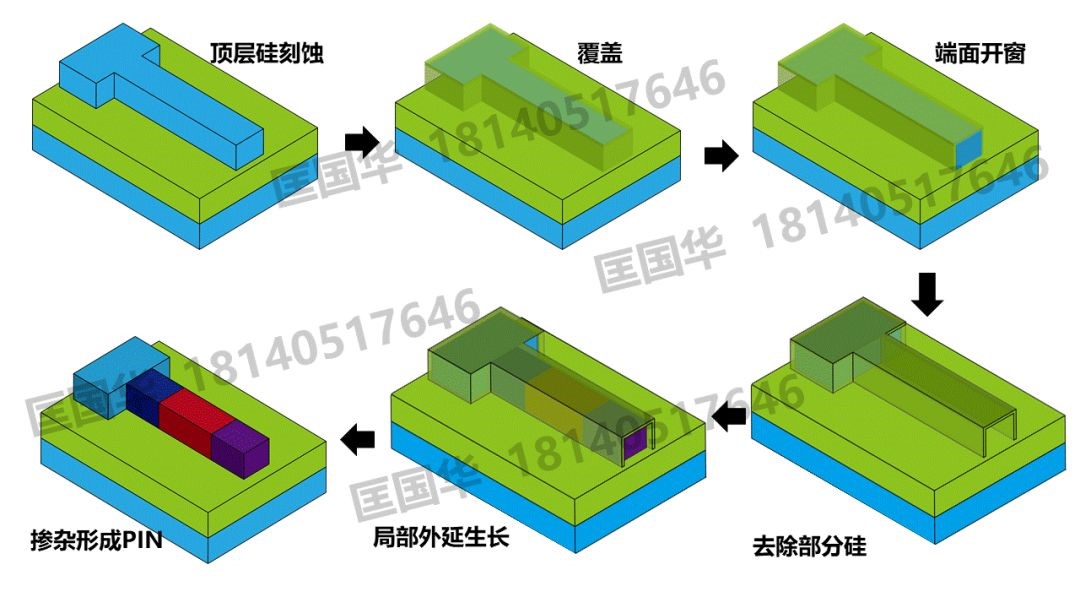

Rockley,他家有个400G、800G和3.2T CPO的集成芯片的图,我们分析了厚硅技术,多模的厚硅如何处理成单模,半环结构的电吸收调制器,以及用的锗硅材料导致的C波段调整的尴尬,因为色散太大,但是这个波段,尤其是加了锗锡材料后,可以无缝衔接到血糖浓度测试等,Rockley要转行了。他家也提出用硅和InP分别做O波段的波导以及调制器,我们专门画了波导和CW光源、光纤阵列以及调制器之间的处理方式。

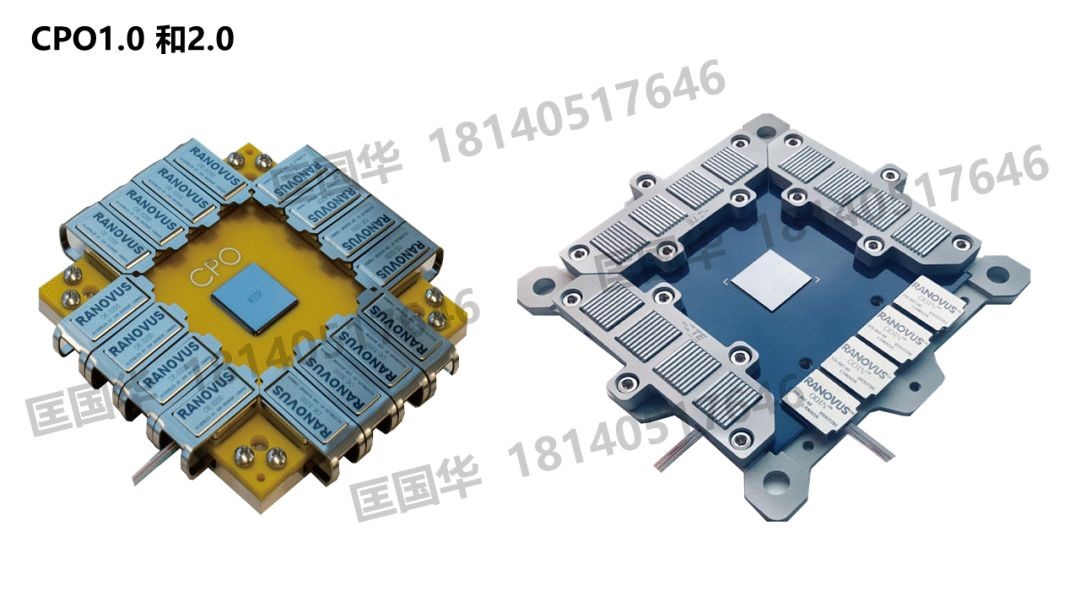

Ranovus,今年是第二代co-packaging,每个引擎3.2Tbps,合起来一共是51.2Tbps,他家的3.2T和Rockley的3.2T不是一个概念,Rockley是每个引擎8通道,每通道25G,合起来一共3.2T,(对一个的是Ranovus的51.2T)

热插拔,

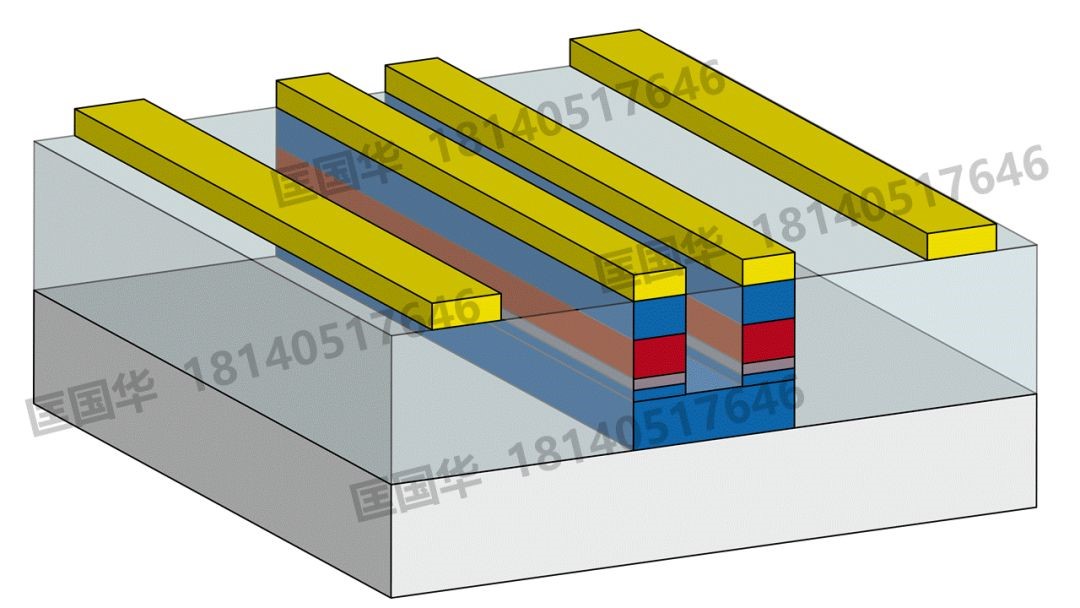

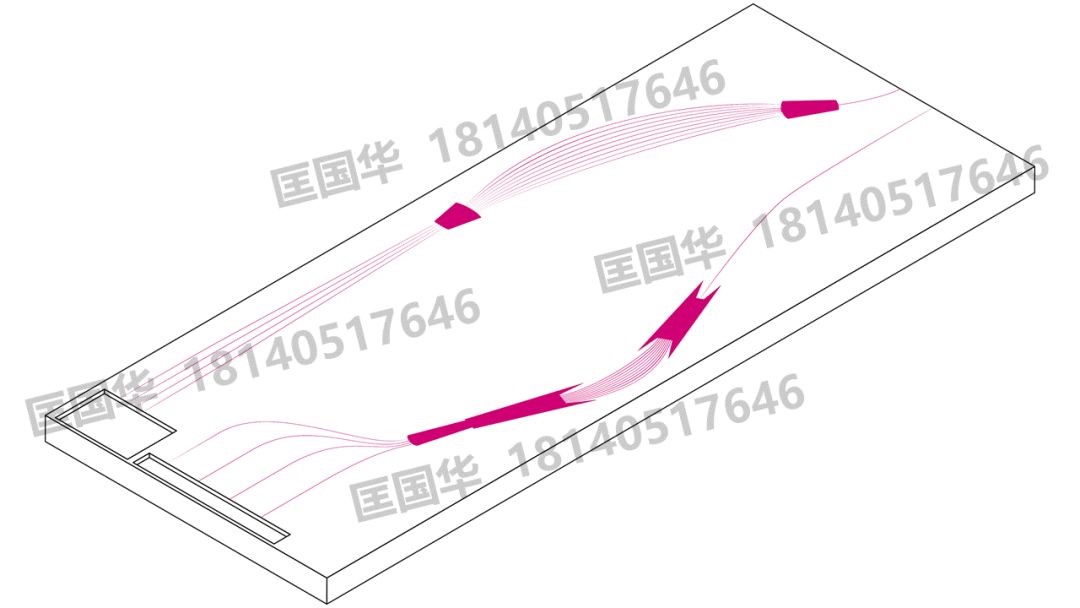

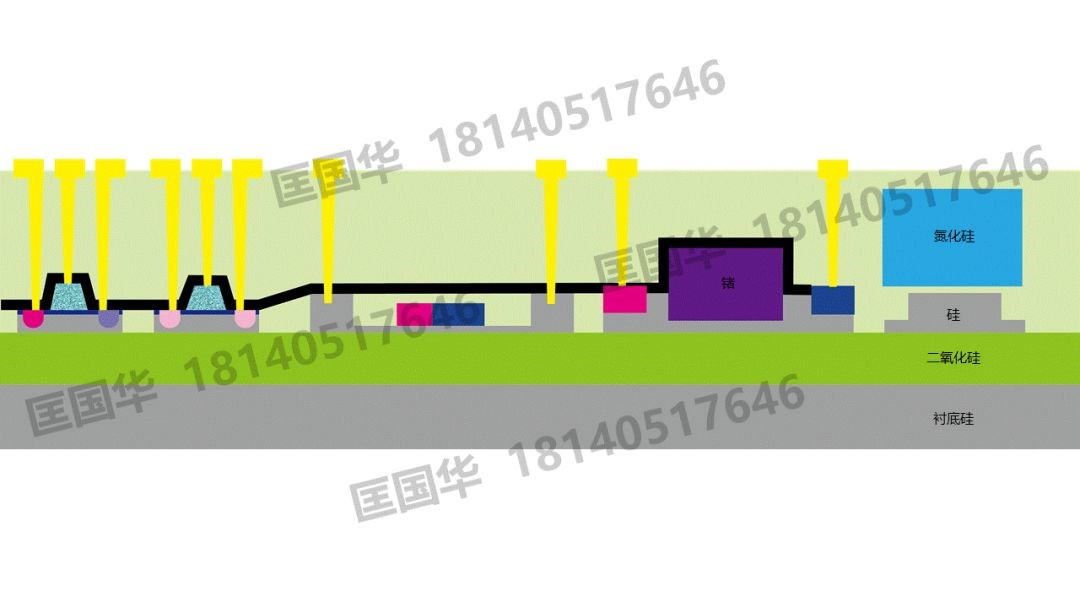

思科,今年有个单通道100G的LR1的方案,MZ调制,分段调制,用多晶硅和栅极做MOS型载流子控制。三层氮化硅做光学耦合,用锗硅做探测器。

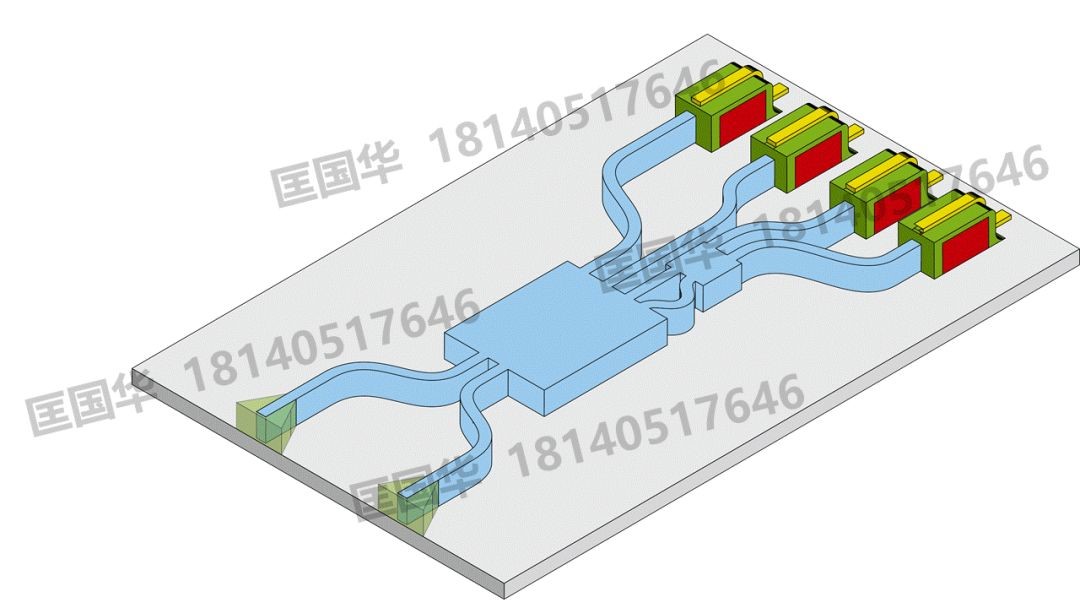

思科收购的Acacia,今年还有个800G的PAM4方案,激光器外置,对接耦合,Y波导分功率给四个MZ调制器,探测器接收用硅波导来做,偏振敏感的处理,是先分偏振,旋转,再接收。

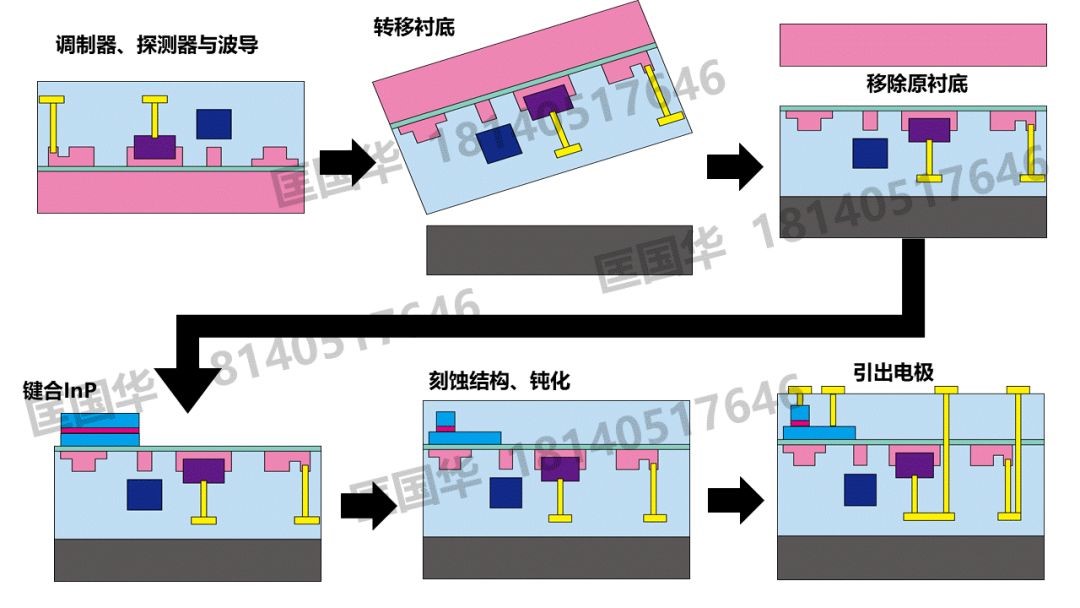

Scintil,他家的激光器,也是异质集成在硅光芯片上的,和Intel的不同是做了更好的气密处理,可靠性更好一些,我们主要花时间来分析他家的工艺路线。

Analog Photonics,热插拔光模块,有400G\800G, 他家和Sicoya、Global Foundries类似,光和电一起处理,但GF家第三代的电,在SOI上做的,而Analog PHotonics是在体硅上做电学,中间掏空一部分,填充氧化硅,做光学部分。

Sicoya的方案,激光器外置,垂直耦合到硅波导上,

聊完co-packaging和Pluggable的高速硅光模块,看下光器件。

InP调制器,

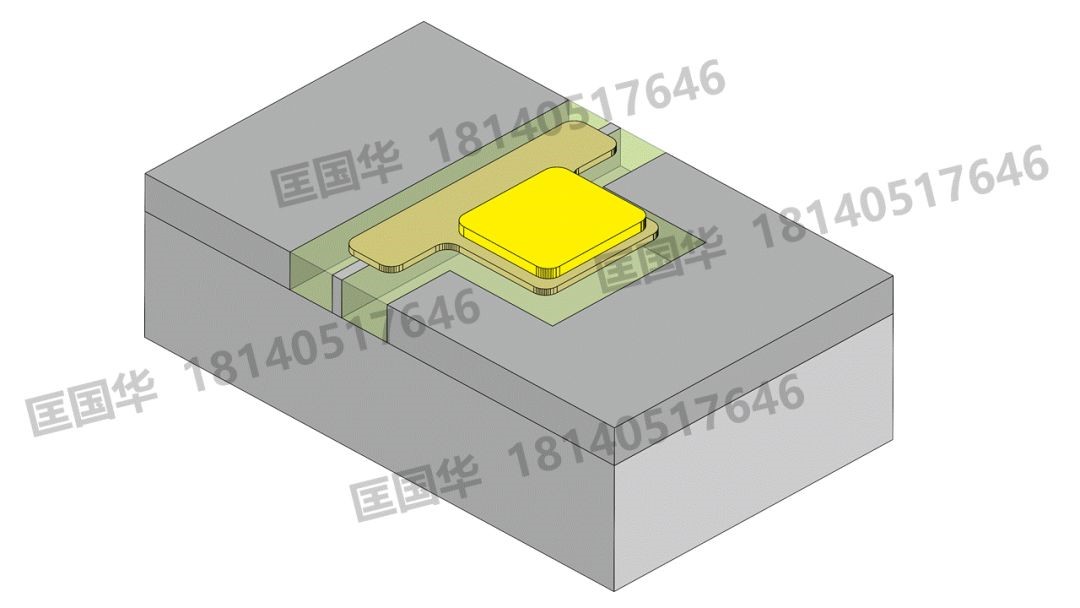

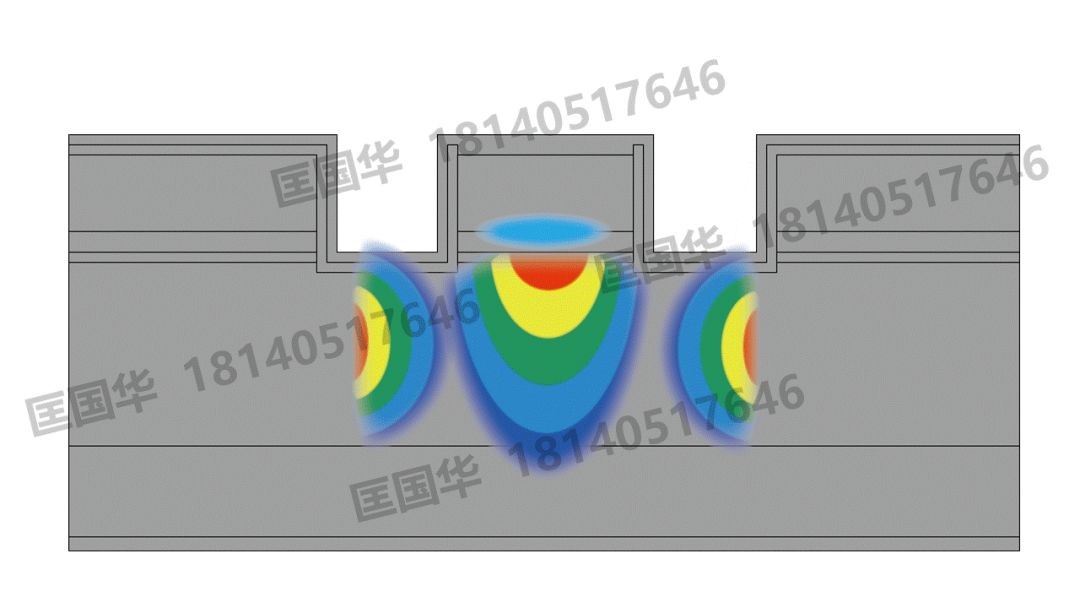

NTT,和Neo等北美厂家的PIN结构不同,用的是NIPN,我们分析PIN、NIN、NIPN几个结构的损耗、速率等不同。

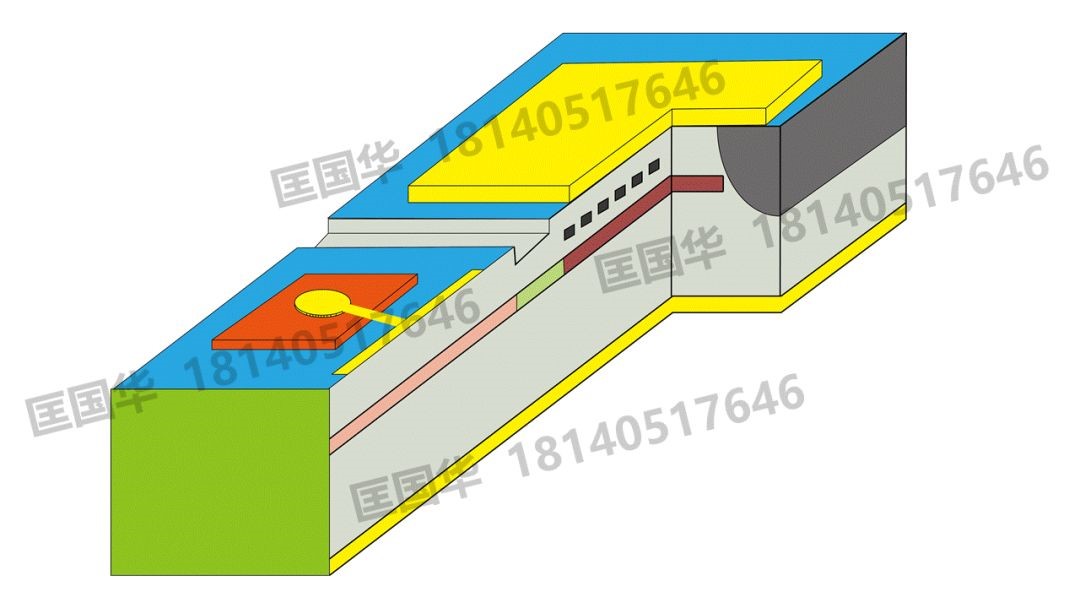

InP的EML,三菱的峰腰式用于800G的单波100G EML,DFB的散热,EAM的高速和强限制处理,波导SSC模斑转换,等等。对增加调制带宽的优化分析。

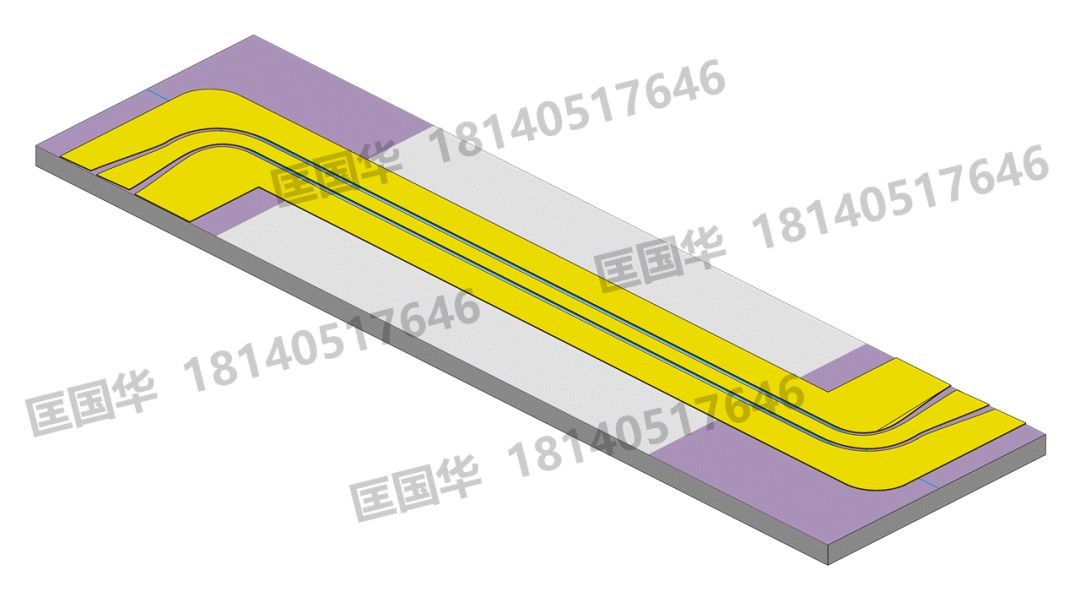

Lumentum的EML,和三菱的EAM的绝缘强限制不同,用的是半绝缘的常规处理,但在焊盘寄生电容下,增加绝缘层,来提高带宽。

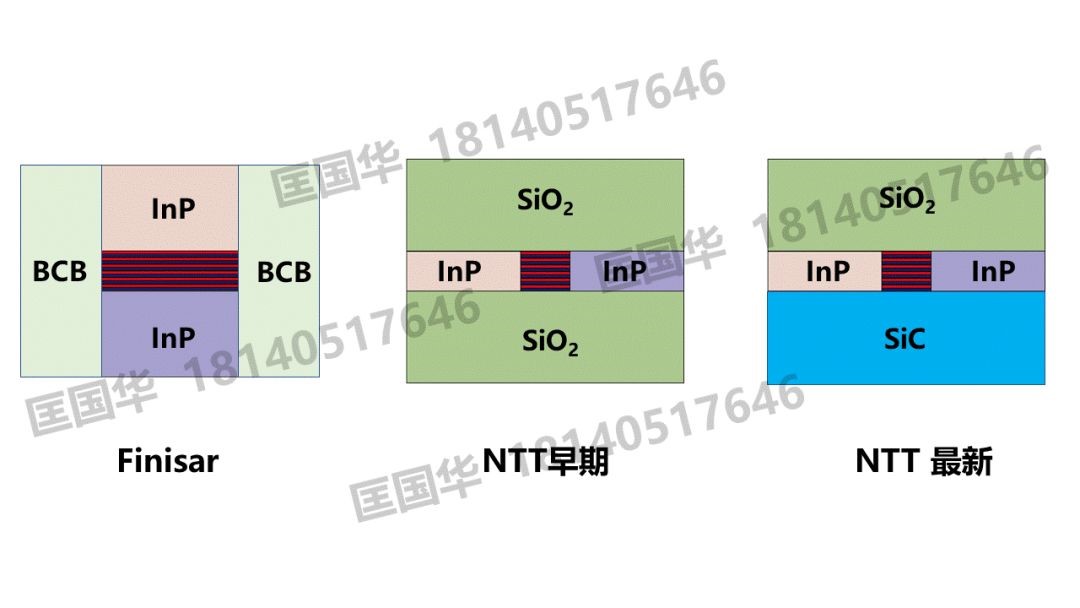

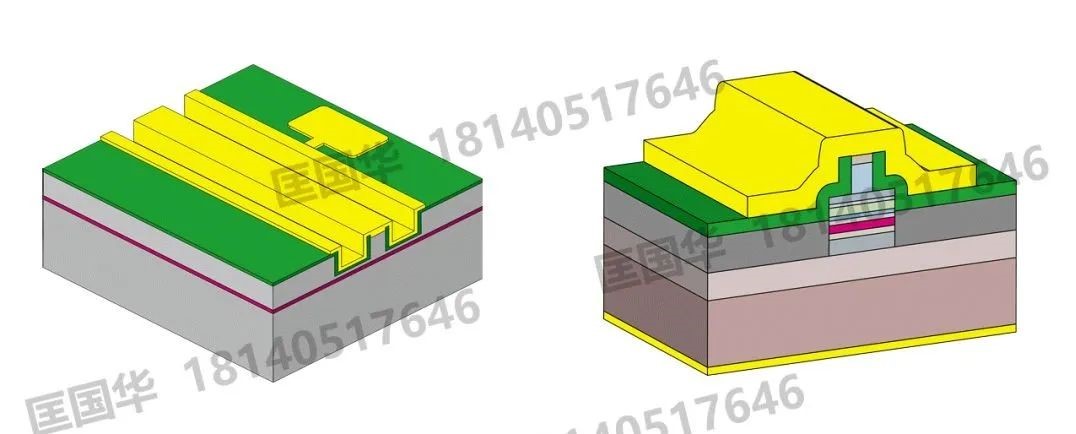

Finisar的,单波100G、单波200G的高速InP DML激光器,BH的BCB强限制,几种PPR带宽提升的处理以及提高抗反射能力,再配合2020 OFC的激光器发布结构,对未来的高密度小型化封装,意义很大。 我们分析他们的量子阱材料,可靠性处理,波导结构的处理和工艺等等

NTT,今年的碳化硅衬底,提高可靠性和带宽,我们对比NTT和Finisar的方案共同点。

Lumentum(原Oclaro),前头OFC做了PN倒置型强限制的高速率结构,今年OFC又回归到传统的RWG结构,目的是用含铝材料提高高温应用场景。

住友,用于800G相干的InP波导型探测器,吸收层减薄,且用吸收层掺杂,提高载流子收集速率,还期待能不降低波导的耦合损耗。

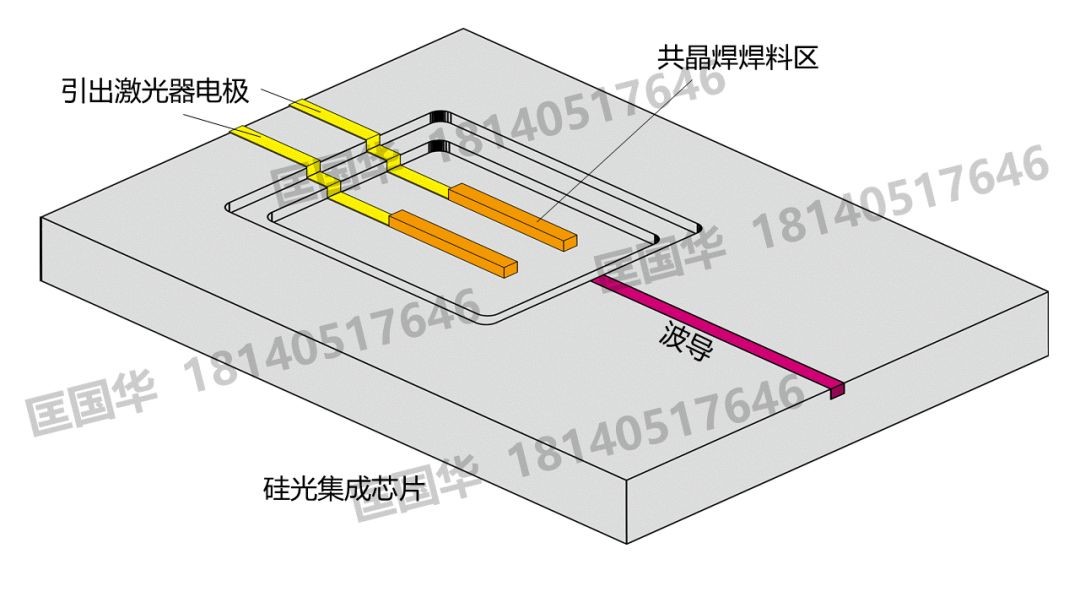

接着就是硅光集成,

IMEC的锗硅电吸收调制器,这个可以和Rockley的做比较。

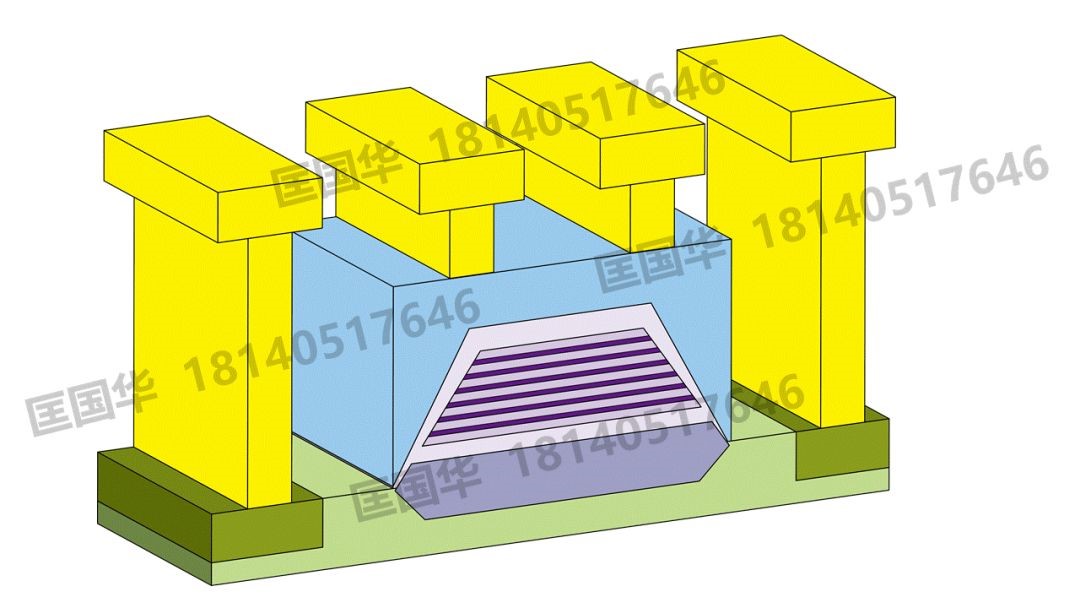

清华大学的,超低半波电压的铌酸锂薄膜调制器,衬底用氧化硅,电极与铌酸锂之间也增加绝缘薄膜,用于拉近电极距离而不至于产生电极的光吸收。

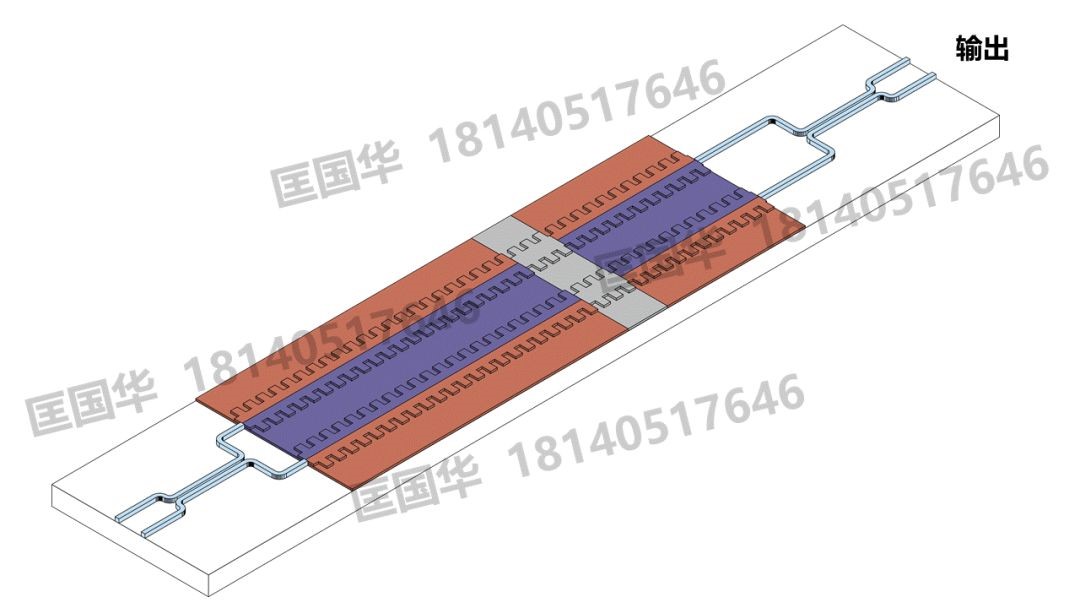

华为和拉瓦尔大学,慢光调制器,功耗低到几乎可以与微环调制器一样,

HPE,用三五族材料来弥补硅的波长敏感性,以便能取消加热环,降低微环调制器的功耗,这个和Intel的做比较。

Ayar Labs,回音壁环形调制,

思科

Intel的单波100G,且偏振不敏感的锗凹陷集成探测器。Intel去年发布的全硅微环双光子吸收功率探测器,用在发射端做功率监控。以前基本上是常见的硅的偏振敏感型探测器。今年是偏振不敏感的硅/锗凹陷探测器

Ayar Labs的辐轮0反偏电压,超低暗电流的探测器。

IBM的辅助模板的PIN型异质集成探测器

思科的氮化硅MZ级联型,工艺不敏感的DeMux器件

POET的氮氧化硅合分波

常规的硅,不发光,需要和激光器集成或Flip chip,或远端连接,

IBM的横向集成结构,

GF的Flip chip结构

早前Macom的flip chip结构,与GF对比

华为的SCOW的七八百毫瓦的超大功率,外置激光器光源,多模激光器发光,但涉及平板滤除高阶模设计,保持单模,降低功率密度,增加输出功率。

Analog Photonics的wafer级对接型检测

Intel的硅与三五族结合工艺,与 Scintil、HPE、IBM等厂的工艺共同点和区别。

光电共共同的集成平台,

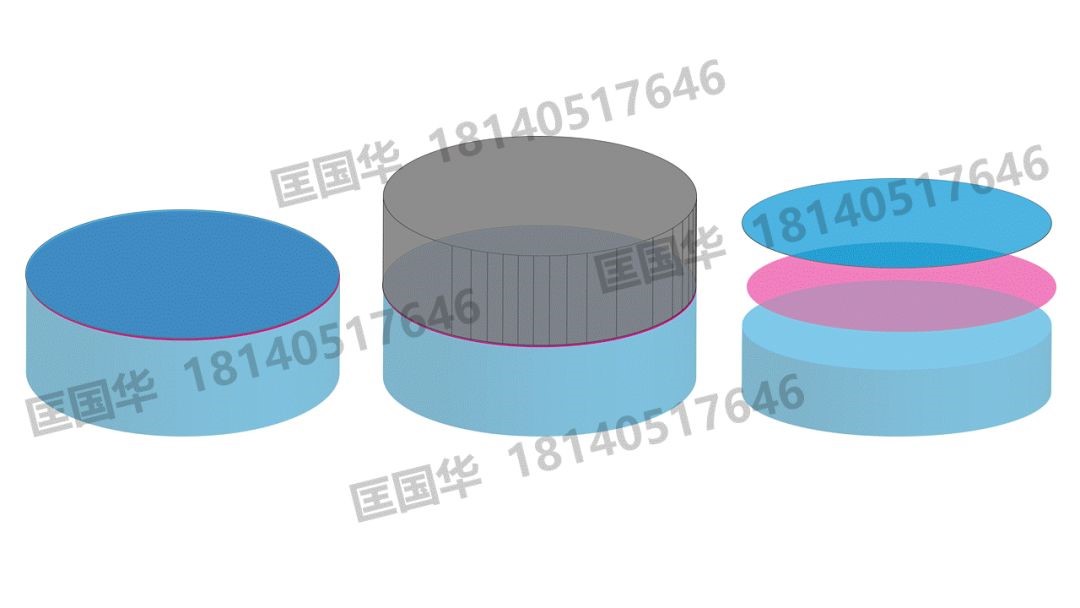

铌酸锂薄膜的微气爆工艺

.....

用了5%的图,略作个概述吧。

我们客服,18140517646